1. 引言

时间间隔测量技术在电子通信、核能科学、脉冲激光测距、电子测量设备、频率综合、医疗设备等研究领域都有着广泛的工业用途。在人员或物体定位系统,例如电力设备巡检实时定位系统中,有时间同步和测距模块,使得时间间隔的测量成为其中关键的部分,定位系统的精度关键取决于时间间隔测量的精度。因而为了达到好的系统性能,提高时间间隔测量的精度至关重要。

目前常用的时间间隔测量方法有如下分类:数字计数器法、模拟内插法、时间幅度转换法、游标卡尺法、“粗”计数和“细”时间测量组合的方法等。为了能同时满足高精度和大量程的需求,目前主流方案是所谓的“粗”计数和“细”时间测量组合[1] ,这里“粗”计数即数字计数器法,采用格雷码计数器实现,“细”时间测量依靠内插技术。本文着重研究基于门延时的延迟线内插技术(又称为时间数字转换器TDC: time-to-digital converter),通过对一种典型的延时链的片上实现,验证和分析时间间隔测量系统性能的影响因素。

2. 时间间隔测量原理

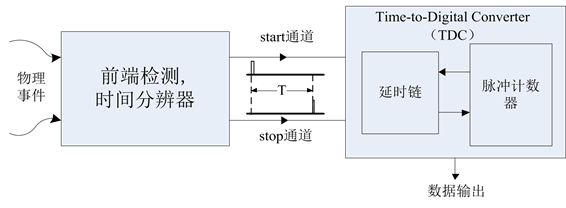

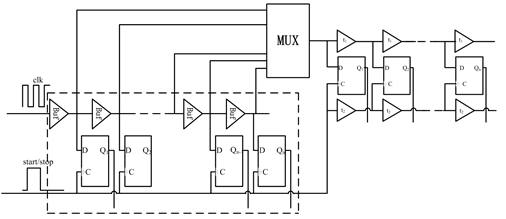

延迟线内插法实现时间间隔测量包含粗测和精测两部分。待测时间T定义为输入给start和stop通道的两个脉冲的上升沿之间的时间间隔。这个时间间隔通过TDC模块来测量,包括脉冲计数器和延迟链,见图1。

时间间隔测量系统有如下几个关键特征参数[2] :精度/分辨率/最低有效位,最小可测量间隔,测量范围,单脉冲精度,噪声,差分非线性,死时间与测量率,功耗,PVT工艺拐角稳定性等。

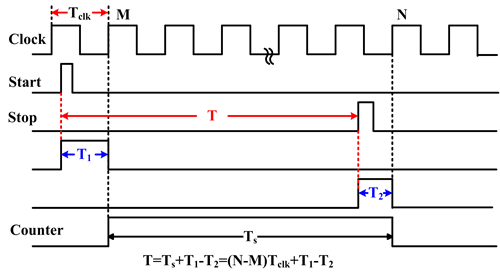

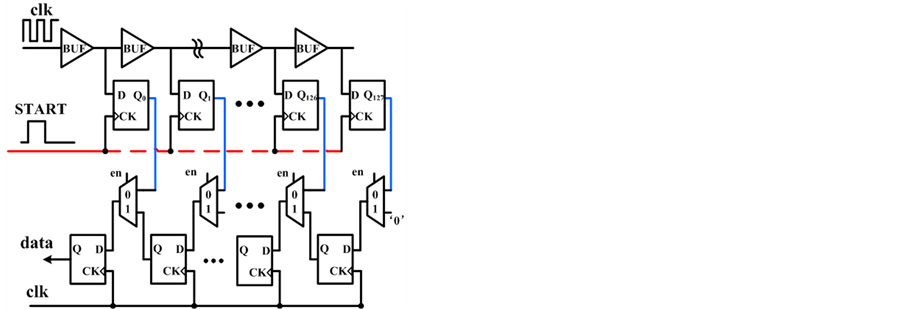

延迟线内插技术能使得时间间隔测量系统在大的测量范围内,保证精确的分辨率和单脉冲精度。图2

Figure 1. Scheme of time interval measurement with delay line interpolation

图1. 延迟线内插法测量时间的基本原理图

Figure 2. Sequence diagram of time interval measurement with delay line interpolation

图2. 延迟线内插法测量时序图

显示了测量时序图,采用经典三段模式:分别测量Ts, T1, T2。

这里,记计数器粗测时间为Ts,测量整数倍时钟周期;记start信号上升沿与其下一个最近时钟上升沿的时间间隔为T1,而stop信号上升沿与其下一个最近时钟上升沿的时间间隔为T2。若start和stop上升沿过后,下一个最近的时钟上升沿分别为第M个和第N个时钟周期,则计数器测得值 ,待测时间间隔

,待测时间间隔 。

。

Start脉冲和Stop脉冲之间的间隔转化为三部分,将参考时作为中间比较信号。粗测量时间间隔由时钟计数确定,不足一个时钟周期的精细测量部分由延迟线确定。T1和T2不足一个时钟周期,采用内插法精测。由于采用时钟作为中间比较信号,所以需要两组测量电路才能分别确定出和T1和T2,在实际芯片设计中实现了两组的延时链和移位寄存器,并让二者对称。

3. 延时链的选取

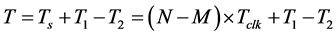

本文所采用的基于门延时的时间数字转换是在获知逻辑门绝对传输延时情况下,通过计算信号通过逻辑门的数量,来精确量化时间间隔的。常用的延时链结构有[3] :基本延时链结构,游标差分延时链结构,带DLL延时链结构[4] ,带PLL延时链结构[5] ,两级延时链结构(图3)。

对于基本延时链,方便实现,算法简单,并能达到基本的精度要求。将参考时钟clk作为反相器链输入,将start信号作为D触发器链各个C输入端。从结构上看,start同时输入所有C输入端,而clk经过不同数目的Buf延时单元进入D触发器链各个D输入端,再通过寄存器观察在start上升沿时D触发器各输出端电平。

4. 芯片实现

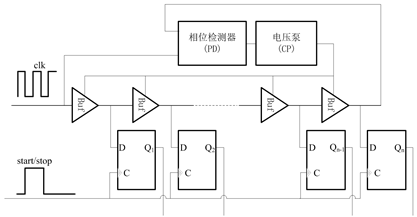

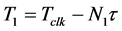

本文实现了基本延时链结构的片上实现,采用0.18 um COMS工艺,完成了128级延时链结构。单个延时单元包括一个D触发器和一个buffer,使用两级反相器作为一个缓冲延时,电路原理如图4。由于start信号要同时接入所有D触发器,为了避免在导线上的差异造成D触发器时钟不同步,在时钟树的实现时采用完全对称的结构。

参考时钟将作为缓冲器链的输入,经过级联缓冲器的推进作为D触发器的D输入端,Start脉冲作为D触发器链的CK输入端,D触发器对延时链采集电平。从D触发器链采集到128个电平值,根据这一组电平值,即可以确定精测值。为了测量方便,将128个电平值传到移位寄存器中,进行并串转换。移位寄存器高位补零,先输出低位数据,再输出高位数据。

D触发器中各电平并行输出,记输出值为Q0到Q127,则对移动的周期信号即时钟,在某个固定点

(a) 基本延时链结构 (b) 游标差分延时链结构(t1 < t2)

(a) 基本延时链结构 (b) 游标差分延时链结构(t1 < t2)

Figure 3.

图3. 不同延时链结构图

Figure 4. The delay chain schematic of this chip

图4. 芯片延时链电路原理图

即Start脉冲的上升沿观测,经过更多BUF输出的时钟,看到的电平值对应原信号波形处在更加滞后的位置,如图5所示。

从图5可以看出,在Start上升沿观测,时钟和经过第一个延时单元、第二个延时单元之后的信号输出电平为“0”;经过3~11个延时单元后的信号输出电平为“1”;之后又有一段“0”的出现。clk在第13个和第14个延时之间经历了翻转,则说明Start在时钟信号clk经过13个延时单元后,Start和距离最近的上一个clk的上升沿重合。对应图2中的T1,计算为:

(1)

(1)

是一个延时单元的延时,N1即测量值13。

是一个延时单元的延时,N1即测量值13。

同理,对于D触发器CK端输入Stop信号,若测得clk电平在经过第N2和N2 + 1个延时单元时由高电平跳变为低电平,则有:

(2)

(2)

为提高测量精度,保证Start脉冲信号同时进入到各个D触发器的时钟输入端,电路和版图需要严格保证信号通路的对称性,如图6所示。

脉冲信号从外部输入,然后一分为二,总共128路,则一分为二后左右两路各为64路。然后再两两对称拆分,一分为二,二分为四,四分为八,如此类推,到最末端。D触发器链的输出,采用相应位数的移位寄存器将并行输出变为串行输出,在FPGA中处理数据从而得到测量值。图7是芯片的整体版图。

Figure 5. The output waveform of the delay line interpolation

图5. 延迟线内插法输出波形图

Figure 6. Symmetrical balance signal path

图6. 平衡对称的信号通路

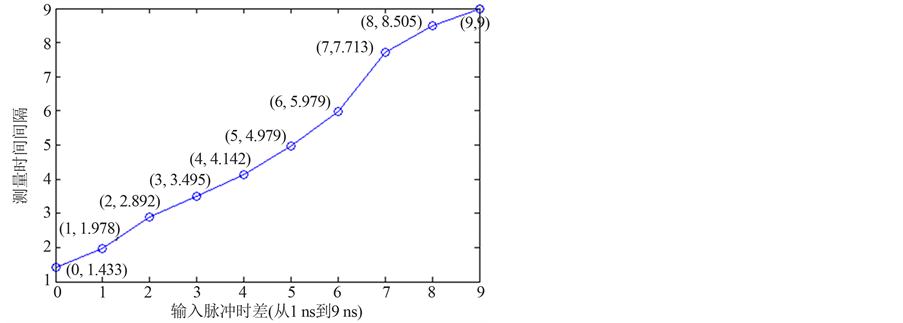

Figure 8. Measurement results of time interval from 1 ns to 9 ns

图8. 输入时差为0 ns~9 ns的测量结果

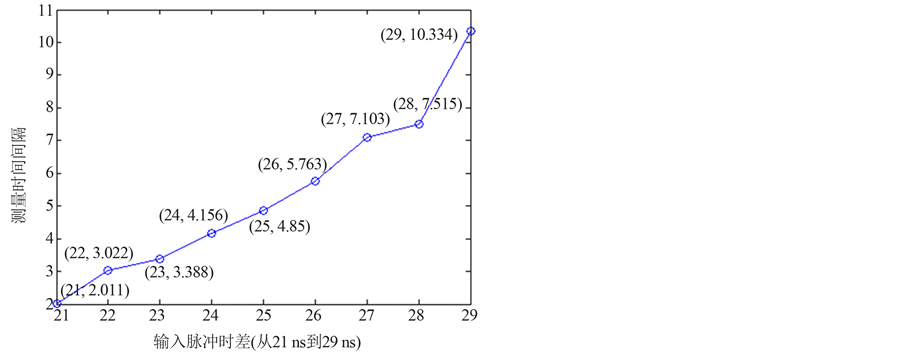

Figure 9. Measurement results of time interval from 21 ns to 29 ns

图9. 输入时差为21 ns~29 ns的测量结果

5. 芯片测试

为了保证测试结果的精确性,采用高精度的脉冲信号产生仪器安捷伦81160A产生频率100 M,占空比为1:1的时钟信号,以及start、stop信号,采用逻辑分析仪观测和采集信号。信号发生器分别产生时间间隔为1 ns~9 ns以及21 ns~29 ns脉冲信号时,芯片测得的实际结果如图8和图9。受工艺、电压、温度等影响,实际测试结果与设计有一定偏差,测量精度在1 ns以内。

6. 结束语

本文完成了延迟线内插法精细测量部分ASIC实现的设计、流片及测试,最终测试精度达到1 ns以内,该电路可集成到定位芯片中,通过检测信号到达芯片的时间差(TDOA)来确定目标的距离,实现目标定位。

基金项目

广西电网,“输变电环境关键技术研究”,GXYT(S)-2013-011TP;国家高技术研究发展计划(863计划)(2011AA010404)。