1. 引言

本文致力于解决系统时钟高精度和高稳定度的问题。通过UM220IIIN双系统接收机和FPGA的结合,输出北斗/GPS中精度最高的秒脉冲作为时钟源,若两者的秒脉冲都失效,就利用FPGA来预测下一时刻的秒脉冲输出作为时钟源。

本文的创新在于不仅仅用单一的卫星授时,而是利用了北斗与GPS两者结合进行授时 [2] [3] ,从而能极大的避免信号丢失情况的发生,实现具有高稳定性和高精度的同步时钟源。而且当两者的秒脉冲都失效时,就根据本地晶振具有短时稳定性来利用FPGA内部自带的高频时钟以及历史数据,预测下一时刻的秒脉冲作为输出。

2. 系统总体方案

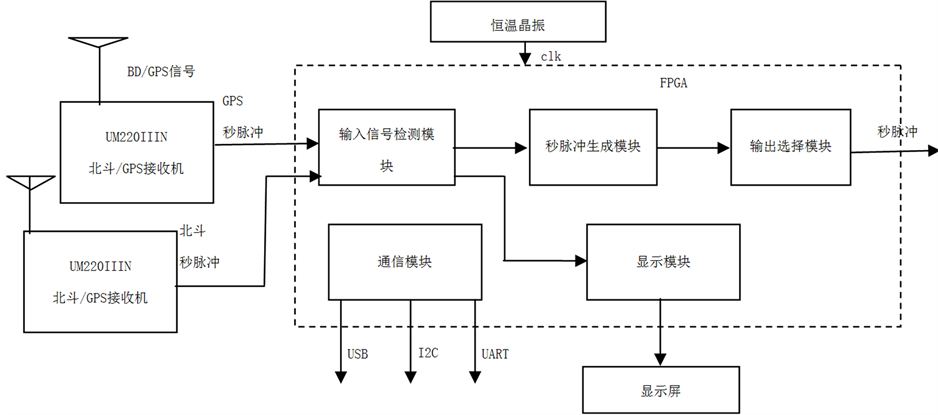

高稳时钟源方案如图1所示,共包括9个模块:北斗、GPS卫星信号接收天线模块,UM220-IIIN双系统接收模块,恒温晶振时钟模块,显示模块,通信模块,输入信号检测模块,秒脉冲生成模块,输出选择模块。

接收天线实时采集卫星信号,并将信号传输到UM220-IIIN双系统接收模块,接收模块将采集到的卫星信号,解码输出两路标准秒脉冲到FPGA模块。在FPGA模块中,首先对输入的两路秒脉冲进行有效性判断,当判断为无效信号时,丢弃输入信号。如果输入被判定为有效信号,那么将对10个秒脉冲周期进行高频计数,求其平均值,以减小随机误差。然后传输到秒脉冲生成模块 [4] [5] ,将生成的秒脉冲信号输入到信号检测模块,这个模块主要完成秒脉冲上升沿的判断,将判断结果输入秒脉冲生成模块,重新生成两路稳定的高精度秒脉冲 [6] 。新生成的高精度秒脉冲将被送入输出选择模块,输出稳定和精度更高的秒脉冲 [7] 。

通信模块主要负责FPGA与其它模块的通信,可选为PC机或其它控制模块。两个模块的通信通过I2C,UART或者是USB。显示模块用来显示秒脉冲输出状态,如显示北斗/GPS有效,或其中某一信号有效。

2.1. 输入信号检测模块 [8]

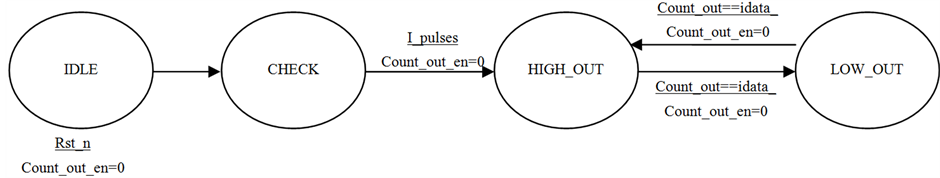

UM220-IIIN双系统GNSS接收模块接收到北斗和GPS卫星信号后,会输出两路秒脉冲到FPGA模块中的输入信号检测模块。如图2的状态转移图所示,在一路输入信号检测模块中,系统在未启动前处于待机状态,数据属于初始化状态,外置的count_high和count_low值保持不变,始终为1。当系统启动后,状态机状态从IDLE等待状态跳转到开始状态。

如果检测到输入的秒脉冲i_pulses为高电平时,状态机从开始状态跳转到高电平计数状态,并输出count_high_en高电平,开始对秒脉冲高电平时间进行计数。当输入秒脉冲由高电平转换为低电平,出现脉冲信号下降沿时,如果count_high正处于大于9,990,000并且小于10,001,000范围,那么判定输入信号为有效信号。这时状态机状态从高电平计数状态跳转到低电平计数状态,并且将count_high_en拉低,count_low_en拉高。如果出现下降沿时,count_high不处于大于9,990,000并且小于10,001,000范围,那么判定输入信号为无效信号。状态机从高电平技术状态跳转到开始状态,并将count_high_en拉低。在低电平计数状态时,和高电平计数状态一样,输入秒脉冲状态跳转时,出现脉冲信号上升沿,如果低电平计数器count_low正处于大于9,990,000并且小于10,001,000范围,那么判定输入信号为有效信号。状态从低电平技术状态跳转到高电平计数状态。

如果检测到输入秒脉冲为无效信号,输入检测模块将发出BD/GPS无效信号到下一级模块。

Figure 1. General scheme of high stable clock source

图1. 高稳时钟源总体方案

Figure 2. State transition diagram of receiver module

图2. 接收模块状态转移图

如果输入的北斗秒脉冲信号有效,那么会将北斗秒脉冲高电平计数器和低电平计数器的值存储进BDpulses_fifo中,当BDpulses_fifo内存储的值满60个时,即北斗秒脉冲输入有效满一分钟时。将BDpulses_fifo内的数据读取出来,求出每个北斗秒脉冲的均值,并将得到的均值存储进BDdata_fifo中。同样的方法,求出每一个GPS秒脉冲的均值,并将得到的均值存储进GPSdata_fifo中。比较两路数据均值的方差,判断输入秒脉冲的精度那一路更高,发出BD/GPS选择信号给下一级。

2.2. 秒脉冲生成模块

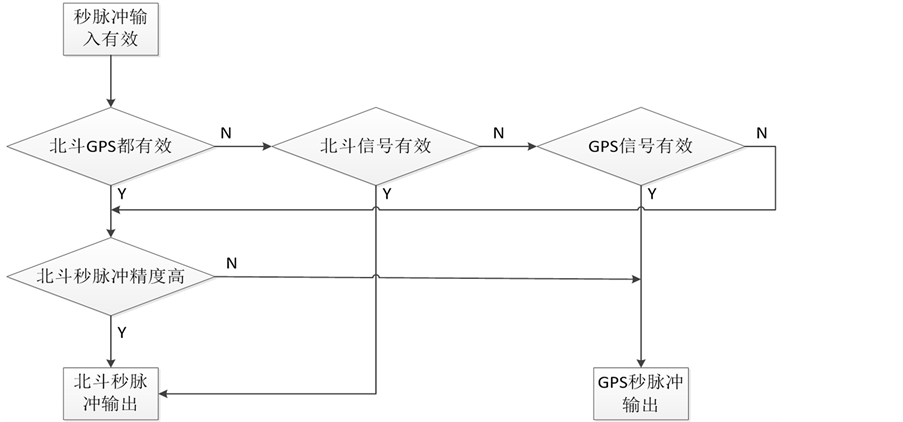

系统启动后,秒脉冲生成模块系统将会从IDLE状态转移到CHECK状态。CHECK状态的作用是确定输出秒脉冲信号的上升沿,确保输出秒脉冲信号与输入信号同步。当检测到输入信号的上升沿后,系统马上从CHECK状态转移到高电平输出状态,并且将count_out_en拉低。在高电平输出状态,count_out计数模块对脉冲输出高电平时间进行计数,当count_out数值等于输入检测模块生成的统计均值时,系统从高电平输出状态转移到低电平输出状态,并将count_out_en拉低,将count_out计数器的值清零。在低电平输出状态,计数器对脉冲输出的低电平时间进行计数,当count_out数值等于输入检测模块生成的统计均值时,系统从高电平输出状态转移到低电平输出状态,并将count_out_en拉低,将count_out计数器的值清零,如图3所示。

秒脉冲生成模块包含两个子模块,分别对应北斗秒脉冲输出和GPS秒脉冲输出。两路输出的方式相同,和状态转移图一致,只是判断状态跳转的阈值不同。

2.3. 输出选择模块

输出选择模块的功能是对两路输入秒脉冲进行判断,选择精度高的一路作为输出。输出选择模块的流程图如下图4所示。在系统启动后,首先对秒脉冲输入有效性进行判断。只有当输入秒脉冲有效时,即秒脉冲生成模块已经开始生成高精度的秒脉冲信号后,才开始进行输出选择。

3. 系统验证仿真

3.1. 逻辑验证

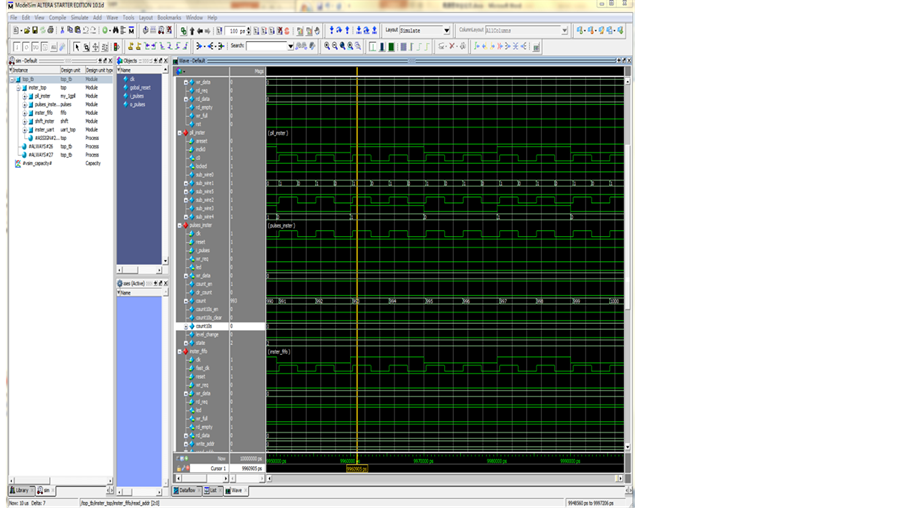

由于整个系统工程较大,所以可以分模块进行验证仿真。QUARTUS II与仿真软件modelsim有很好的兼容性,可以在QUARTUS II中编写验证代码,直接调用modelsim进行逻辑仿真验证。

时序逻辑仿真,首先要建立仿真文件,模拟实际电路的输入信号,并输出到系统工程文件中。编译后,调用modelsim进行时序逻辑的仿真。进入modelsim之后,需要将待观察的参数添加到波形栏,并建立好分组,如下图5所示。重新添加参数后,对modelsim中的文件重新加载,再次运行,就能观察到系统对应的时序逻辑。观察时序波形是否与设计的相符,如果不相符,则需要找到误差参数,并对工程文件进行修改。修改工程文件后,不能直接在modelsim中仿真,需要在QUARTUS II中对系统工程文件进行编译,生成对应的时序链接。

3.2. 实际电路验证

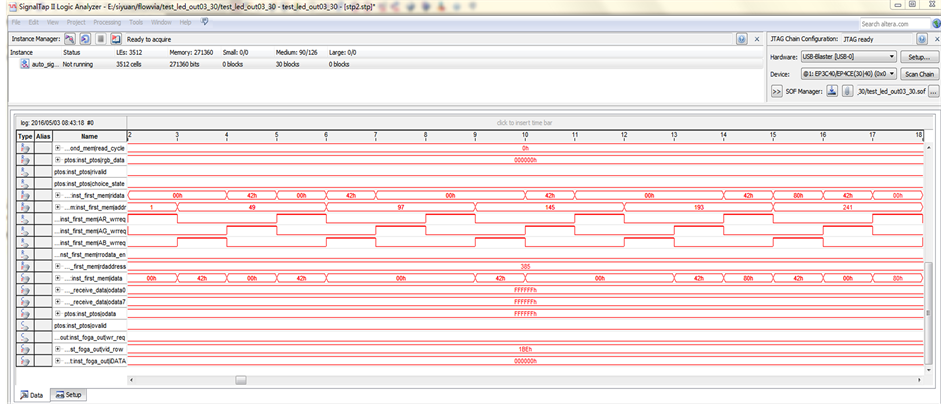

当时序逻辑验证通过后,表明电路逻辑不存在问题,但由于实际电路因为布局布线,噪声干扰等原因,存在信号延时。所以虽然时序逻辑验证通过,还不能代表系统能正常工作,仍需要进一步验证。QUARTUS II自带的signaltap仿真软件,能够采集FPGA上电运行的实时数据,并将数据以波形的方式反映出来。调用signaltap采集信号的界面如下图6所示。

3.3. 实验结果

图7展现出高稳频率源样机的总体图,其中绿色的为UM220双系统接收机,先通过接收机采集北斗/

Figure 3. State transition diagram of second pulse generation module

图3. 秒脉冲生成模块状态转移图

Figure 4. Flow chart of output selection module

图4. 输出选择模块流程图

Figure 5. Simulation waveform of modelsim

图5. Modelsim仿真波形

GPS信号,然后把秒脉冲输入到FPGA板上,最后通过FPGA的代码实现功能,从而输出精度最高的秒脉冲作为时钟源。

图8表示为高稳时钟源输出的高精度同步秒脉冲在示波器上的显示结果。

Figure 6. Acquisition signal interface of signaltap

图6. Signaltap采集信号界面

Figure 7. Prototype of high stable clock source

图7. 高稳时钟源样机

Figure 8. Oscilloscope display experimental results

图8. 示波器显示实验结果

先通过UM220双系统接收机接收到北斗/GPS信号,然后把输出同步秒脉冲送进FPGA中,在FPGA对输入信号(即北斗/GPS的秒脉冲)进行处理后,选择精度高的同步秒脉冲输出,并用示波器显示出来。

4. 结论

通过实际电路验证并结合分析实验结果,表明“基于北斗/GPS秒脉冲的高稳时钟源设计”可以解决系统时钟高精度和高稳定度的问题。

基金项目

国家自然科学基金 (61004123);广西大学大学生创新项目(T3070098228)。