1. 引言

RS422串行总线采用差分传输的方式,其传输速率最大可达到10 Mbps。因其总线的可靠性、通信协议的简单性以及对硬件要求不高,所以在当前各类工业系统平台上具有广泛应用。

当前,现有的大多数串口服务器采用USB转串口的模式,该模式存在两点不足:无法实现较长距离的数据传输和无法完成非标准波特率的串口数据传输 [1] [2] [3] 。

针对此状况,本文研制一套基于Xilinx公司的Zynq芯片为核心的多功能串口服务器。该服务器由以太网口转换出多个RS422串口(以下简称422),既通过网线实现了长距离数据传输,又充分利用Zynq的灵活架构,完成了标准和非标准波特率兼顾的422串口数据传输。

2. 组成框图及原理

2.1. 组成框图

多功能串口服务器组成框图如图1所示。

Figure 1. Multifunctional serial-port server structure

图1. 多功能串口服务器组成框图

2.2. 工作原理

多功能串口服务器以Zynq为主控核心,主要功能是通过网口接收计算机的指令,并将指令解码分发给各422端口,同时将各422端口的返回数据打包,再通过网口反馈给计算机。

当前,Zynq作为Xilinx公司新一代的FPGA,内部除了常规的FPGA的资源外,还集成了ARM硬核,这使得其既具有通信和控制上的灵活性,同时也具有逻辑上的实时性。基于该平台的串口服务器,充分利用了Zynq内部的这两种资源,并通过AXI (Advanced Extensible Interface)总线完成两种资源之间的数据交互,实现了波特率的动态重配,同时也实现了特殊波特率通信。

首先,计算机通过以太网与Zynq中的ARM进行通信,然后ARM通过内部AXI总线与FPGA进行数据交互,最终再由FPGA来完成对外的422数据输入输出。

数据下传时,ARM通过以太网获得计算机端数据,经解码和校验正确后,会根据数据包中格式字的不同被分为三种类型:指令包、标准波特率422数据包和非标准波特率422数据包。其中,指令包用来对串口的通信波特率、校验等进行配置;标准波特率422数据包则在ARM中进行打包,然后通过AXI总线传输给FPGA,并调用FPGA中的IP模块axi_uart16550,将数据进行串行化并输出;非标准波特率422数据包同样也在ARM中进行打包并通过AXI总线传输,但由于FPGA中的axi_uart16550只能完成标准波特率的数据传输,所以,针对所需要的非标波特率,需在FPGA内采用自定义模块,根据协议来完成数据的串行化,并分配给相应的端口输出。

数据上传时,首先由FPGA从各个端口接收串行数据,同样,包括标准和非标准波特率422串行数据,标准波特率的由IP模块axi_uart16550完成串并转换并通过AXI总线传输到ARM,非标准波特率则采用用户自定义的串并转换模块完成转换,再通过AXI总线传输给ARM。上传数据在ARM汇总后,进行重新打包,再通过以太网传输至计算机。

3. 设计实现

3.1. 硬件及接口设计实现

硬件系统采用Xilinx公司的Zynq系列XC7Z020为核心,配合相应的外围驱动及接口芯片构建。框图如图2所示。

Zynq系列作为Xilinx公司新一代的FPGA,其内部由两个主要部分组成:一个由双核ARMCortex-A9构成的处理系统和一个等价于一片FPGA的可编程逻辑部分。另外还具有集成的存储器、各种外设和高速通信接口等 [4] 。

FPGA部分适合用来实现高速逻辑、算术和数据流子系统,而ARM支持软件程序和操作系统,这使得任何被设计的系统功能可以恰当地在一块芯片上做出硬件和软件之间做出划分。FPGA和ARM之间的链接采用了高速的工业标准的高级可扩展接口AXI连接方式,如图3所示。

为提高Zynq输出接口的驱动能力,硬件设计上采用了TI公司的74lvc164245数字驱动芯片,不但提高了接口驱动能力,同时对外起到隔离保护作用。接口芯片的作用则是完成信号的差分和单端之间相互转换的功能。

3.2. ARM部分设计实现

ARM部分的编译环境采用了Xilinx SDK®。设计中,ARM作为一个中间单元,充分发挥其在通信上的灵活性,调用其中的网口驱动子模块,来完成与上位机的通信 [5] [6] [7] 。为提高通信速率,网口通信协议采用UDP格式。由于UDP协议本身存在信息传输上的不可靠性,所以在用户层的信息帧格式中,添加了帧流水号和帧尾的和校验。

为使得系统兼顾专用性和通用性,在设计上,将422分为两部分实现。一部分422驱动内核采用ARM实现,另一部分则采用FPGA实现。工作中,ARM接收计算机通过网口发送来的指令帧和数据帧,若为指令帧,则解析出指令帧中的指令码,根据指令码的不同来完成相应的工作,这其中包括:串口选择、串口配置(波特率,校验方式配置)等;若为数据帧,则分两种状况:标准波特率422数据帧,先在ARM中完成422的协议实现,然后经由AXI总线传输给FPGA来最终输出(由于系统中,Zynq的422对外接口均是从其FPGA部分的硬件管脚引出);如果是非标准422数据帧,则ARM不做处理,直接打包通过AXI总线传输给FPGA,由下级的FPGA负责协议实现和驱动输出。

3.3. FPGA部分设计实现

FPGA作为ARM的下游设备,负责高速和通用422信号的最终对外交互,编译环境选用Xilinx公司的Vivado®。

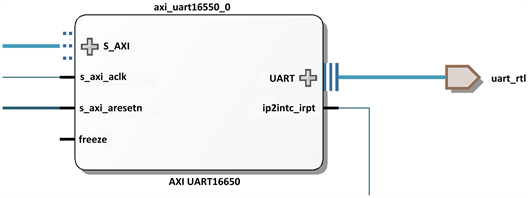

标准波特率422信号驱动协议层已由ARM部分完成,串行数据通过AXI总线传输给FPGA。在FPGA端,只需在图形界面Block Design中,调用AXI总线IP模块axi_uart16550,如图4所示,便可将该串行指令通过FPGA的硬件端口uart_rtl对外进行数据交互 [7] 。IP核的个数根据422端口需要可配置多个。这一类串口的特点是:协议层由ARM完成,灵活性强,可通过网口动态重配。

Figure 4. Core of axi_uart16550 IP

图4. axi_uart16550 IP核接口图

由于ARM受到内部寄存器配置及工作时钟的限制,所以无法驱动和处理一些非标准波特率的串行信号。而FPGA因其具有很好的实时性和灵活的时钟配置,使得在一些特殊以及较高波特率的工程应用中,就需要由其来完成底层协议工作。系统中,首先,由ARM判断解码出来的数据,如果属于非标准波特率数据,则直接打包,通过AXI总线发送给FPGA进行处理。FPGA在收到总线上的数据后,先进行解码,解析出需要串行化输出的数据(数据位宽一般为8bit),然后,按照设定的波特率将数据串行化输出到芯片引脚。同样,在接收外部输入的串行数据时,FPGA采用特定的波特率时钟对串行数据进行并行化处理,转换成8bit位宽的数据,再进行打包,通过AXI总线传输给ARM。FPGA的底层驱动程序中,有一个模块专门负责生成串口波特率时钟,其基本原理是采用时钟计数的方式,根据工程需求,灵活配置波特率 [8] [9] 。

4. 实验验证与分析

针对标准和非标准波特率的端口,采用了两种不同的通信回路进行实验验证。

4.1. 标准波特率通信实验验证

该类端口的验证采用了USB转422数据转接器来进行辅助验证。具体连接关系如图5所示。

Figure 5. Connection for standard baud rate test

图5. 标准波特率验证实验接线图

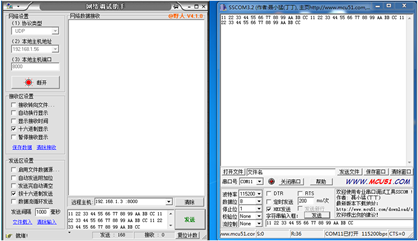

实验中,用网线将串口服务器和计算机相连接,然后将一路422端口波特率配置为115,200 bps,再通过USB转422数据转接器连接至计算机。计算机端采用网络调试助手发送数据,串口调试助手接收返回的422数据,测试结果如图6所示。图中,左侧的网口发送数据和右侧串口接收数据一致。

Figure 6. Transmitted data of Ethernet and received data of 422 serial port

图6. 以太网发送和422串口接收数据对比图

4.2. 非标准波特率通信实验验证

由于采用的非标准波特率,所以无法接至计算机端采用串口调试助手进行观测,所以实验中采用路由器自闭环的方式进行验证。具体连接关系如图7所示。

Figure 7. Connection for non-standard baud rate test

图7. 非标准波特率验证实验接线图

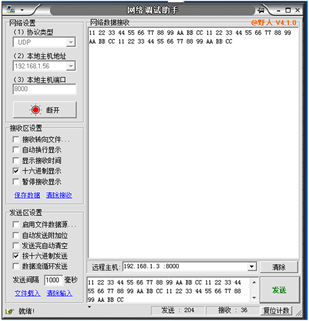

实验中,用网线将串口服务器和计算机相连接,然后将通信接口1的一路422和通信接口2的一路422波特率配置为2 Mbps,并在硬件接口处闭环短接(通信接口2的422线路进行了收发交叉)。计算机端采用网络调试助手发送和接收数据,测试结果如图8所示,图中,下方的发送数据和上方的接收数据一致。

Figure 8. Transmitted data and received data of Ethernet

图8. 以太网发送和接收数据对比图

4.3. 实验结果分析

上述实验结果表明,该串口服务器可实现标准和非标准波特率的发送和接收,且数据传输稳定。

5. 结论

相比于市场上的大多数采用USB转串口的服务器,该服务器采用了以太网,实现了长距离的串行数据传输;同时,相比于现有的只采用FPGA或微处理器实现的串口服务器,多功能串口服务器在设计过程中,充分利用了Zynq中ARM内核和FPGA内核各自的优势,既实现了串口波特率的动态可重配,又实现了非标准波特率的串口通信。

参考文献