摘要: 随着信号技术的发展,函数信号发生器已成为测量领域不可替代的仪器。但如今业界生产的信号发生器大多体积庞大,且便携不易。本文介绍一种基于EP4CE10F17C8N现场可编程门阵列和AD9708数模转换器的便携式信号发生器。通过锁相环技术和DDS技术的应用,它可以产生正弦波、三角波、方波、梯形波等常用信号发生器,并且可以改变占空比、频率、电压等一系列信号参数。此外,在某些特殊情况下,用户可能需要输出特殊波形。基于这个特点,它具有允许用户根据自己的意愿更改波形的功能。通过应用此技术,我们观测到了不同种类的输出波形,实现了输出信号的个性化。

Abstract:

With the development of signal technology, function signal generators have become irreplaceable instruments in the field of measurement. But most of the signal generators produced in the indus-try today are bulky and not portable. This article describes a portable signal generator based on the EP4CE10F17C8N field programmable gate array and the AD9708 digital-to-analog converter. Through the application of phase-locked loop technology and DDS technology, it can generate common signal generators such as sine wave, triangle wave, square wave, trapezoidal wave, etc. and can change a series of signal parameters such as duty cycle, frequency, voltage and so on. In addition, in some special cases, the user may need to output a special waveform. Based on this fea-ture, it has the ability to allow the user to change the waveform according to their wishes. By ap-plying this technique, we can observe different kinds of output waveforms and realize the individ-uation of output signals.

1. 引言

在电路学习和设计过程中,需要各种调试设备。有些设备不仅占用了大量空间,而且价格相对昂贵。因此,对于电子相关专业的学习者来说,拥有一个相对较小的调试装置,响应速度快,功能齐全,拥有适当性能的参数,可以提高开发效率,降低开发成本 [1]。现场可编程门阵列(FPGA)是可编程(PAL)、通用阵列逻辑(GAL)和其他可编程器件的产物 [2] [3]。它是专业集成电路领域的半定制电路。与专用直接数字合成(DDS)芯片相比,FPGA具有运行速度快、设计周期短、资源丰富、成本更低的优点。与微控制器(MCU)相比,FPGA并行运行,可以输出多通道且不会受到干扰。一般来说,我们的信号发生器由三部分组成:数字信号发生部分,模拟信号发生部分和电源部分 [4]。

2. 整体系统设计

在数字信号生成部分,我们选择使用Cyclone IV E系列的FPGA芯片EP4CE10F17C8N。在模拟信号生成部分,使用ADI公司(ADI)的高速数模转换器(DAC) AD9708将数字信号生成为模拟模型,并设计低通滤波器以防止噪声干扰,然后通过运算放大器电路实现硬件幅度调制功能。电源部分,我们设计了两种供电模式:9 V锂电池和USB供电。我们将芯片与五个按钮连接,一个用于系统复位,另外四个用于信号调整 [5]。

2.1. 数字信号生成

EP4CE10F17C8N是Altera生产的超低成本、超低功耗FPGA。它是大批量、成本敏感型应用的理想选择。它具有10,320个逻辑单元,414 kbs嵌入式存储资源,23个18位 × 18个嵌入式乘法器,2个通用PLL,10个全局时钟网络,8个用户IO库和179个用户I/O。

为了调整波形的频率,我们在芯片中定义了一个定时器。当计时器每次达到计数值时,ROM和RAM将转到下一个地址读取数据。当计数值较小时,读取数据的速度会更快。当计数值为0时,频率达到最大值。因此,频率数值的范围受输入时钟的限制。

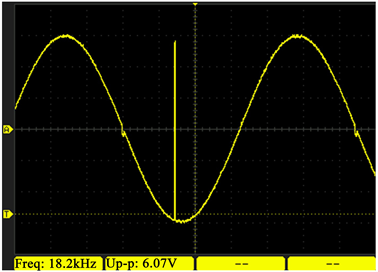

至于生成用户暂时需要的任意波形,我们调用RAM IP核来使用芯片的内部RAM。初始化系统时,写入MATALAB生成的MIF文件,其每个位地址上的数据为0。由于RAM允许用户在运行过程中写入数据,因此,我们设置了绘制波形的模式,让用户更改RAM每个地址上的数据。然后,FPGA叠加从RAM和ROM读取的数据,并将它们输出到DAC芯片。自定义波形的效果如图1所示。

Figure 1. A picture of the custom waveform

图1. 自定义波形的图片

2.2. 模拟信号生成

AD9708是ADI公司生产的TxDAC系列高速数模转换器,具有高性能、低功耗等特点。AD9708具有8位数模转换,最大转换速度为125 MSPS (每秒百万个样本)。

DAC的外围电路由低通滤波器和运算放大器电路组成。低通滤波器的作用是防止外部噪声的干扰。信号通过低通滤波器后,通过高带宽运算放大电路,实现将差分信号转换为单端信号的功能。并在输出端连接压敏电阻以调节电压,因此,输出电压根据需求从−5 V到+5 V变化。

2.3. 模拟信号生成

为了实现系统便携性,我们使用9 V锂电池和USB电源,以满足用户的不同需求。输入电压转换电路如图2所示。

Figure 2. Voltage conversion circuit diagram

图2. 电压转换电路图

3. 锁相环的应用

锁相环(PLL)是一种反馈控制电路,它可以通过使用外部输入参考信号来控制内部振荡信号的频率和相位。锁相环的结构如图3所示。

我们使用主频率为50 MHz的时钟。当ROM地址为32位时,我们可以得到1.56 MHz的稳定且无失真的正弦波,宽度为32位。此时,频率数值的上限受FPGA芯片主频的限制。因此,我们使用PLL将时钟频率提高到400 MHz。但这并不是本芯片PLL输出时钟的极限,即402.5 MHz。我们之所以没有将时钟频率发挥到极限,是因为当我们把频率提高到400 MHz时,当FPGA的PLL输出达到极限时,会受到实际硬件约束的限制。芯片内部很难达到时序稳定,因此,正弦波开始不稳定。32位正弦信号在400 MHz时钟频率下的输出可以达到12.5 MHz。此时频率范围可以达到从1到12.5 MHz的信号,足够满足大多数简单的需求。

4. DDS的应用

纸型、页边距与版式

DDS是一种通过相位合成所需波形的频率合成技术。DDS将上一个时钟周期生成的相位数据反馈给加法器,使其在下一个周期中与频率设置数据一起添加。同时,DDS将数据发送到转换电路,然后通过DAC和LPF(低通滤波器)输出模拟信号(见图4)。

由于AD9708是一款没有DDS内部集成的芯片,我们提前通过MATLAB生成各种常用波形的MIF文件,通过调用ROM IP核将文件写入芯片的内部ROM,输出信号时依次根据ROM地址读取数据并发送到ad9708,从而模拟DDS的功能。因此,我们可以存储我们认为预先常用的任何波形。如前所述,我们还可以通过读取和写入RAM来更改波形。

5. FPGA工作过程

系统有四路输入,分别是按键、用户波形变化数据、系统时钟、系统复位键信号。内部有七个模块,分别是键控和去抖模块、PLL时钟模块、时钟切换模块、RAM模块、ROM模块、数据读取和数据处理模块以及模拟信号输出模块(见图5)。

5.1. 密钥和去抖动模块

此部分是用户控制信号输入的主要部分,它由四个键组成。当按下键时,由于键的物理结构,会出现抖动。通常,将使用物理电路或软件方法来消除按键反弹的影响。但是我们选择通过软件方法消除影响,这里我们使用三个寄存器来记录与关键状态相关的数据。我们使用计时器。当用户按下键时,键状态改变,键计时器开始计时,寄存器用于记录键状态。如果未达到计数值,则输入键状态随记录的计数值而变化,计数器再次开始计数,并将新状态记录在寄存器中。然后我们使用两个寄存器,一个用于记录关键输出数据,另一个用于标记数据的有效性。

当计数器达到计数时,将密钥状态分配给密钥输出数据寄存器,并将数据有效性寄存器标记为true。然后计数器再次开始计数,数据有效性立即标记为false。通过这种方式,实现了消除关键抖动的功能。我们使用两个寄存器来记录与模式相关的数据,一个用于记录当前模式,另一个用于记录开关状态。

5.2. 锁相环时钟模块

该模块采用PLL原理,将50 MHz的主频提高到400 MHz,然后输出两个不同频率的时钟。

5.3. 时钟切换模块

我们使用的时钟主要来自PLL通过主频率和主频率时钟生成的时钟。有两个问题需要解决,一个是PLL时钟的初始化,另一个是时钟切换过程中产生的毛刺。PLL时钟需要大约100 ns的时间来初始化,因此,我们应该避免在开始时直接使用生成的时钟信号。切换时钟时,应避免直接切换,因此,我们添加一个D触发器,将切换动作延迟一个周期。

5.4. 内存和只读存储器模块

我们将不同的波形数据依次放入ROM的256个地址中。当我们输出不同的波形时,我们只需要将读取地址切换到下一组256个地址。至于RAM,复位信号连接到RAM,这有助于快速清除用户设置的波形。图6显示了设备输出的不同波形。

Figure 6. Pictures of different output waveforms

图6. 不同输出波形的图片

5.5. 数据读取和数据处理模块

该部分负责DDS中累加器和相位寄存器的功能。将按键的状态输入到模块中,选择系统模式,并更改每个模式的设置。我们将系统分为四种模式:波形切换模式、波形绘制模式、频率调节模式和时钟切换模式。在波形切换模式下,系统允许我们读取ROM地址。在波形绘制模式下,用户通过前两个按钮选择要调整的数据地址,第三个按钮增加当前所选地址的数据以调整波形。严格来说,频率调节模式和时钟切换模式都设置了频率调节,但是通过调整时钟可以在很宽的范围内快速进行频率切换。

5.6. 模拟信号输出模块

这是FPGA中输出信号的最后一个变化,它将来自RAM和ROM的数据叠加在一起,然后将上述方法调整的频率输出到DAC。

6. 结论

信号发生器是电路学习不可或缺的工具。但是市场上主要流通的信号发生器往往有高成本、功能单一的局限性。基于低成本和便携性,本文提出一种变频变周期的便携式信号发生器。通过实验模拟,输出了不同种类的波形,实现了控制波形的个性化。

致谢

感谢2020年大学生创新创业训练计划项目。