1. 引言

在现代通信应用领域中,通信环境复杂,调制与解调作为数字通信系统的重要组成,其性能至关重要 [1] 。DQPSK调制解调方式具有抗干扰能力强、频带利用率高等优点,在现代数字通信系统得到了广泛的应用,实现对接收信号的准确解调,高精度、实时、快速的解调算法一直是人们的研究热点 [2] 。传统的软件无线电平台、天生的串行运行机制难以满足FIR滤波、FFT等运算密集型任务的需求,而FPGA实现方案具有定制性强、量产较小、迭代需求快、体积小等多种优点,故本设计采用FPGA设计软件无线电收发系统,具有较强实用性。

2. DQPSK调制原理及设计

数字相位调制技术即相移键控是一种载波相位随着基带信号的变化而在不同相位之间切换的调制方式。正交相移键控是利用四种不同的载波相位来表征四种数字信息 [3] 。对于输入的二进制数字信息,将其相邻数字两两组合,一共可以得到四种不同的组合方式,然后分别用四种不同的载波相位与之对应。QPSK已调信号由两路正交的BPSK信号合成,且这两路信号具有相同的基带调制波形。QPSK信号可以表示为:

(1-1)

式中,g(t)为发送码元序列,

为信号的符号采样间隔,

为载波角频率,

为第n个码元的载波相位值。

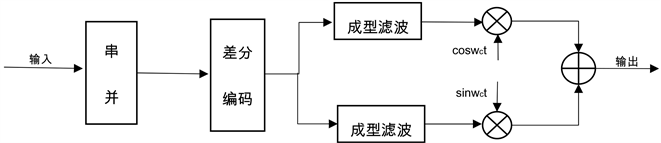

由于QPSK系统是利用接收载波的绝对相位值来对调制信息进行判断,容易因外界因素的影响而产生相位翻转,即相位模糊,所以常用相对相移方式代替绝对相移方式,对四进制数据进行差分编码,从而形成了差分四相相移键(DQPSK) [4] 。DQPSK是利用前后码元的相对相位变化关系来表示信息的QPSK信号,通常可用直接调相法、插入脉冲法和相位选择法产生,本设计选用直接调相法,采用两路正交调制的方式,即分别对基带信号进行I路调制和Q路调制,然后将两路和载波相乘后的信号进行相加。DQPSK信号调制流程框图如图1所示。

Figure 1. DQPSK modulation flow chart

图1. DQPSK调制流程图

先由串/并变换电路将输入的二进制双极性不归零数据逐个分为两个并行序列,再进行差分编码,将绝对相位转换成相对相位再进行调制。基带信号傅里叶级数展开在频域上频带是无限宽的,波形延伸至其他码元,脉冲波形就会重叠,造成码间串扰,通过成型滤波可以一定程度地减小码间串扰,从而提升误码性能。在实际工程中,通常应用具有升余弦频谱特性的滚降滤波器,其频域传输函数为 [5] :

(1-2)

式中,

为滚降系数取值范围为[0, 1],

为码元持续时间,

为信号频率。

升余弦滚降低通系统的带宽如式所示 [6] :

(1-3)

频带利用率如式所示:

(1-4)

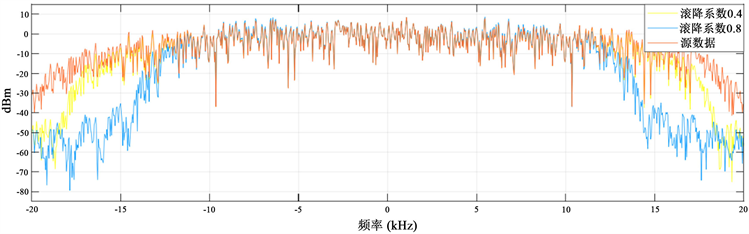

可以看出,滚降系数

越大,

衰减越慢,占用带宽

越大,频带利用率越小,引入的噪声越多,滚降系数

越小,则波形中的高频分量越少,越接近理想低通滤波器,波形拖尾较长,在进行数字信号截断处理时容易造成信号能量损失,因此在实际工程中需要均衡

的取值 [7] ,对成型滤波器进行MATLAB仿真,从图2可以明显地看到成型滤波器的限带作用,本设计综合考虑码间串扰,选择滚降系数

为0.8。

Figure 2. Response spectrum diagram of different roll-off coefficients

图2. 不同滚降系数的响应频谱图

3. 载波同步原理及设计

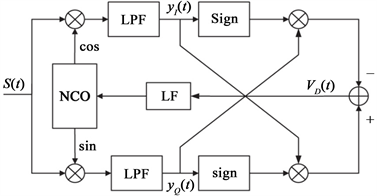

解调就是从接受信号中恢复出原始基带信号的过程,解调分为相干解调和非相干解调,相干解调性能更好,本文选择的解调方式为相干解调。接收机在进行QPSK数据相干解调时,本地振荡信号需要与接收信号的载波具有相同的频率和相位,再将调制信号与本地参考载波相乘进行相干解调,这样才能恢复出正确的数据,这种利用接收信号恢复出本地震荡信号的方法叫做载波同步。目前常用的载波恢复算法有M次方环法、逆调制环、科斯塔斯(Costas)环法等 [8] 。Costas环又称同相正交环,利用锁相环提取载频,不需要对接收信号作平方运算就能得到载频输出,易于硬件实现,在实际工程中被广泛应用,故本设计采用Costas环完成载波恢复。Costas环原理如图3所示。

Figure 3.The basic structure of the Costas ring

图3. Costas环的基本结构

设输入已调信号表达式为:

(2-1)

其中,

、

为信号的幅度,

为载波频率,

为信道传输过程中所产生的相位误差,压控振荡器输出的载波信号为

,经过90˚相移得到:

,

为输出载波与输入信号载波的相位误差。

本文对传统Costas环进行了改进,鉴相器模块采用面向判决的鉴相器取代了传统的乘法鉴相器,此鉴相方式相比基础Costas环降低了计算量,又保留了一定的鉴相精度。改进后的Costas算法结构如下图4所示。

Figure 4. The structure of the improved Costas algorithm

图4. 改进后的Costas算法结构

将输入信号分别与本地振荡器输出的同相和正交信号相乘,再分别通过低通滤波器将混频后的信号中的高频分量滤除,得到包含同相支路误差信息的信号

和包含正交支路误差信息的信号

,符号函数运算和相乘器、相加器构成了鉴相器,鉴相器输出为:

(2-2)

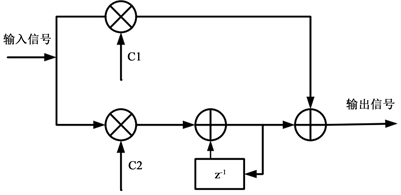

环路滤波器是Costas环的重要组成部分,决定了整个环路的传输特性,数字环路滤波器参数的设计也是锁相环设计的重点和难点。由于理想二阶环路具有优良特性,在锁相环中应用最为广泛,图5为数字环路滤波器的结构图。

Figure 5. The structure of a digital loop filter

图5. 数字环路滤波器的结构

由图可知,其数字化系统函数为:

(2-3)

对于数字环路滤波器来讲,关键问题在于设计

、

,这两个参数决定了环路滤波器的性能,实际工程中

、

的计算公式如下 [9] :

(2-4)

(2-5)

其中,T为系统采样周期,

为阻尼系数,实际应用通常取

,

为环路振荡角频率,

为数控振荡器的相位控制增益,

为鉴相器增益,通常取

,只需确定

、

的值即可确定环路滤波器参数。等效噪声带宽

与

的关系如式(2-6)所示 [10] :

(2-6)

由锁相环工作原理可知,当

(

为调制数据序列的码元符号速率)时环路正常锁定,确定

的值后便可由式计算出

的值。

数控振荡器的增益为 [11] :

(2-7)

式中,

为采样频率,N为数控振荡器的相位累加字长,

为NCO的相位累加字更新周期。

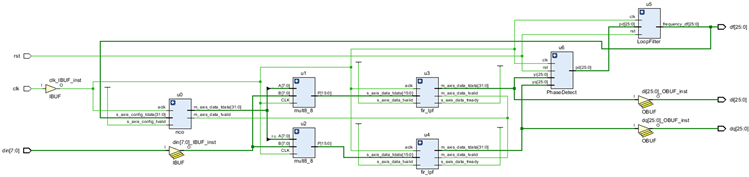

4. 载波同步的FPGA实现

载波同步部分主要由NCO、低通滤波器、鉴相器以及环路滤波器几部分组成。环路中NCO可由Vivado的DDS IP核实现,DDS初始频率控制字的大小与调制端的载波频率大小相同,整个系统的频率由输入的相位增长控制字控制,相位增长控制字经过一个时钟缓存,然后通过一个相位累加器不停计算增长的相位,所有的DDS输出数据都是预先计算好并且存储在查找表中 [12] 。在时钟上升沿,通过这个计算好的累加相位值去查表,然后将查表得到的数进行输出环路中。低通滤波器选择使用FIR IP核实现,滤波器系数由MATLAB将系数量化导入,使用Vivado开发可调用系统已有的IP核实现,不但能够减少工作量提高效率,而且可以保证设计的性能。根据之前的讨论可知,改进后的Costas环鉴相方式主要涉及符号判决、取反和加法运算,鉴相时先判断经过低通滤波器数据的正负,再将此结果与另外一路数据相乘,乘法器会增加环路的数据位宽从而增大Costas的环路增益,从而导致环路无法锁定。鉴相器可用Verilog语言编写,在硬件实现时有符号数的第一位即表示数据的极性,取一路数据的第一位对另外一路数据进行极性操作即可,不需要进行乘法运算,节约了资源。环路滤波器的主要设计在于

、

这两个参数大小的确定,据式(2-4)、式(2-5)可得出

、

的值。在FPGA中对浮点数处理比较复杂,可将

、

的值转换为2的负整数次幂作为近似值运算,此时无需进行乘法运算,可使用移位操作实现。FPGA实现后的RTL原理图如图6所示。

Figure 6. RTL schematic diagram of FPGA implementing carrier synchronization

图6. FPGA实现载波同步的RTL原理图

DQPSK调制算法参数设计如下:符号速率

;输入数据速率

;载波信号频率

;输出数据位宽为16位。

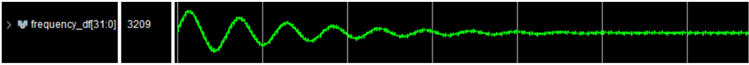

运行结果如图7所示,将调制好的数据输入到科斯塔斯环中,可以看到环路经过了一段时间的调整,相位偏移最终趋于稳定。

Figure 7. Costas ring locking process

图7. Costas环锁定过程

5. 结论

本文主要研究和分析了DQPSK调制解调,设计了调制解调的方案,分析对比了多种载波恢复算法后,选择了最适合DQPSK的Costas环法,并在传统Costas环上进行改进,通过Vivado软件进行开发和仿真,在FPGA上实现了该算法。该方案降低了算法整体的复杂度,节约了硬件资源,且有较好的环路性能,具有良好的应用场景。

基金项目

中央高校基金号2021NYYXS106。