1. 引言

指数衰减信号一般呈现上升快、峰值点窄,拖尾长的特点,导致对该种信号的幅度信息提取难度大。采用的梯形成形算法的原理则是将难以通过采样得到的峰值点拓宽,使得其更容易被采到。该种算法内部逻辑较复杂,但优点是幅度信息准确,能控制梯形参数,参数调节灵活,有效减少由于衰减过程导致基线漂移和脉冲堆积的概率 [1],并且只要对控制好算法参数,就能消除弹道亏损 [2]。本文提出的基于FPGA的自适应梯形成形的算法利用FPGA的并行、高速优势,通过代码将最终成形的梯形信号的上升沿时间、平顶时间、下降沿时间都能确定。并加入了自适应内容,利用输入原信号的特征进行初步计算,进一步得到成形结果,对比结果的特殊点数据,判断是否还需要进行算法参数调整,如此,经过多次迭代,最终实现输出顶部平坦的梯形信号。

2. 梯形成形算法原理

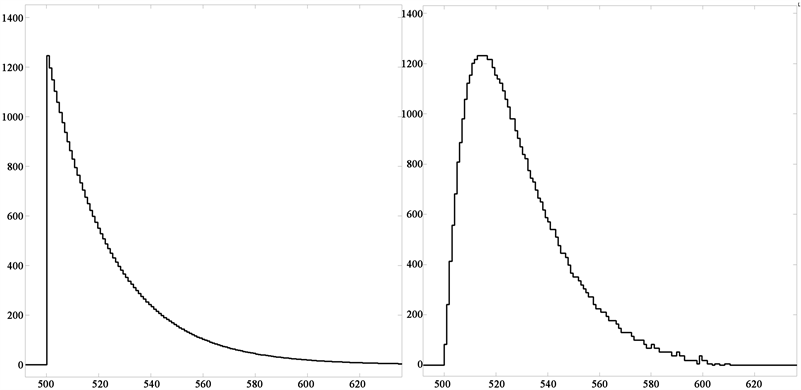

Figure 1. Ideal exponentially decaying signal (left); Actual exponentially decaying signal (right)

图1. 理想指数衰减信号(左);实际指数衰减信号(右)

如图1所示,无论是理想信号还是实际信号,要准确提取到信号的幅度信息,必须要采到对应的时间点,而指数衰减信号从脉冲到来至衰减至0最大只有几个微秒的时间,要在这样的信号中精确采集到峰值点,难度可想而知。

梯形成形算法的目的就是将指数衰减信号滤波成形为上升时间、平顶时间可控等腰梯形。理想研究对象表达式为:

(1)

其中,

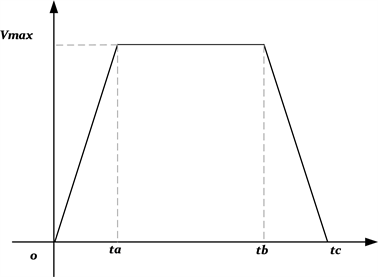

为信号幅度,τ为信号衰减时间常数。输出期望信号图形如图2所示。

Figure 2. Trapezoidal shaping desired output

图2. 梯形成形期望输出

为梯形上升时间,

为平顶时间,

为梯形下降时间,梯形成形算法原理如图3,其表达式为:

(2)

(3)

对等式(1)、等式(2)离散化,再经过Z变换后做商可得到整个系统的传递函数

:

(4)

其中,

为上升沿采样点数,

产生上升沿;

为平顶部分采样点数,

产生下降沿;

,

取1,

用于去除拖尾;

用于匹配时间和幅度;

为反馈部分,用于产生梯形形状;将等式(4)经Z逆变换转换到时域后,可得最终算法的时域表达式:

(5)

3. 自适应研究

1994年。美国的研究员Valentin. T. Jordanov利用ADC进行信号的模数转换 [3],实现数字化指数衰减信号的滤波过程。西班牙的Alberto Regadio等人主要研究了ADC采样频率与梯形成形平顶之间对应关系,提出了实时化自适应数字滤波成形方法 [4];国内关于梯形成形自适应的技术主要是成都理工大学王敏提出双重遗忘法实现了脉冲的基线恢复 [5] [6]、同校的凡小红实现了基于LMS算法的自适应梯形成形算法 [7]。

通过对市面上相关产品的调研,发现对于梯形成形的部分均未实现对不同输入信号进行自适应梯形成形的功能。根据等式(5)可知,算法中参数只有

、

、d三个,一般来说对于不同输入,我们需要控制输出梯形的上升时间和平顶时间一致,即自适应参数只有d。

由于输入信号的τ值不同,直接导致与之有数学关系的d值不同,而传统产品均是在已知输入信号特征的情况下,通过程序来选择算法内设的参数。这种方法的主要弊端有两个,一方面,需要存入足够多的参数用于应对不同的输入信号;另一方面,当一种输入信号随着环境改变而发生波形变化时,显而易见,固定参数无法处理这种情况。此时,就需要有一种算法能根据波形实时特征及时调整成形算法参数d。在设计中通过对脉冲衰减阶段进行采样,采集相邻两个点的数据做商,结果即为d,推导过程如下:

(6)

(7)

(8)

当

时,可得:

(9)

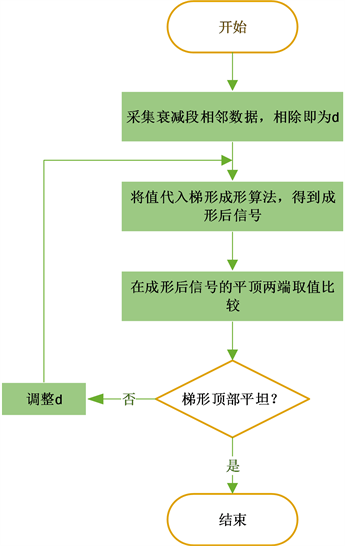

通过求得的d值带入梯形成形算法,得到第一次的成形结果,再按照时序在平顶时间位置采数据对比,如果取得的两个数据相差在允许误差范围内,即认为成形完成,d值为最终成形参数,如果两个数据相差很大,则按照大小关系增大或减小d值,再对输出取样,迭代多次,即可得到最终结果,梯形成形自适应流程图如图4所示。

Figure 4. Trapezoidal shaping adaptive flowchart

图4. 梯形成形自适应逻辑

4. 总体设计

4.1. ADC量化模块

设计的输入信号为连续信号,先在40 MHz时钟下经过12位ADC采样量化,并将量化后的数据送进FPGA中存储器中,以供读取。

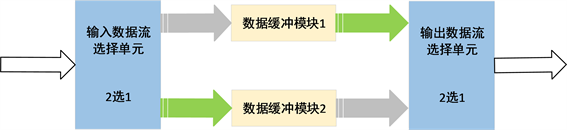

4.2. 离散化数据存取

由于FPGA片内时钟频率为100 MHz,远高于ADC采样时钟频率,为使得数据存取过程不发生丢失,需要对数据进行异步时钟读取,采用典型的乒乓操作存取数据,存取方式如图5所示,通过交叉控制两片双时钟RAM读写使能进行存取,写入时钟为40 MHz,读出时钟为100 MHz。

Figure 5. Schematic diagram of ping-pong operation

图5. 乒乓操作示意图

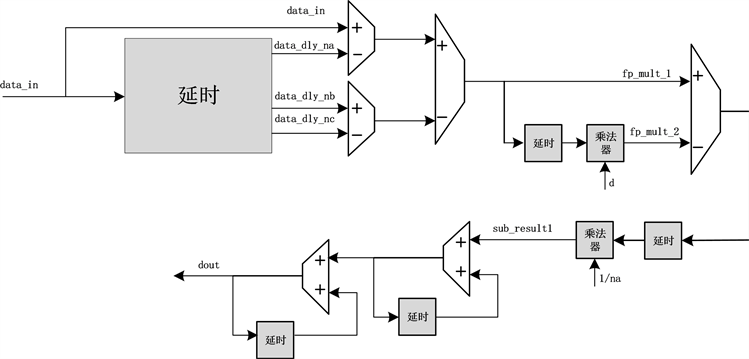

4.3. 梯形成形模块

Figure 6. Trapezoid shaping module flow chart

图6. 梯形成形模块流程图

观察系统函数H(z)的表达式不难发现,此函数具有输出反馈环节,是一个无限脉冲响应(Infinite Impulse Response, IIR)数字滤波系统。为了降低系统设计的复杂度,方便信号的流水线计算,避免整形和浮点数之间转换误差的积累,故选择如图6所示级联结构来实现,仿真中关键信号介绍如表1所示。通过仿真发现,对于线性移不变系统,改变各级联系统的顺序不会影响最终输出的梯形信号,但由于在FPGA中具体实现中存在误差与有限字长效应(主要是把系数d用有限位二进制表示时产生的量化效应),所以必须考虑系统的分解方式与级联顺序。另外对于FPGA内部的浮点数乘法和除法需要特别注意,一般乘法IP核的计算延时(Output Latency)为5至11个周期,而浮点数的除法IP核一般有14至33个周期的延时,为了提高整个系统的实时性,尽量减少除法器IP核的调用。由于模块输入信号为12位整形数据,而参数d一般为0到1的浮点数,为了节省资源、优化时序,故整个模块数据类型为整形–浮点数–整形,在初期将整形运算均完成,将结果转换成浮点数运算,最后再转换成整形,完成反馈及最终输出。

Table 1. Introduction of related signals

表1. 相关信号介绍

5. 仿真测试

仿真部分共分为两个部分,第一部分为MATLAB仿真,以理想信号作为输入验证算法的正确性;第二部分为实际信号输入,先通过MATLAB仿真,再利用QUARTUS II编程和ModelSim仿真软件验证自适应功能。

5.1. 理想信号MATLAB仿真

由图7可知,根据参考文献及相关推导得出的梯形成形公式能够成功将理想的指数衰减信号滤波成形为梯形信号。

5.2. 实际信号MATLAB仿真

利用示波器将实际信号采集下来,存入ROM中,利用编写好的自适应算法,直接将最终的参数d的值作为常数代入仿真,最终真实信号的最大值为1233,而最后成形的梯形平顶高度为2030,根据仿真结果可见,经过梯形成形后的信号,幅度增长较大,平顶明显,梯形特征清晰,图8结果证明,真实信号可以成功成形成梯形。

5.3. 实际信号ModelSim仿真

由仿真输出图9可见,数据与MATLAB输出波形形状吻合,对比数据后,证明数据大小。结果证明设计正确。

6. 结论

本文利用MATLAB软件SIMULINK工具仿真实现了传统梯形滤波成形算法,分析了级联环节的作用,通过增加负反馈环节自适应的调节成形参数以实现梯形输出,增强了该算法的环境适应性;利用Quartus II编写Verilog代码,通过级联方式简化FPGA处理过程,提高了系统的实时性;通过对实际脉冲信号进行采集,经ModelSim仿真得到的测试结果与MATLB仿真结果大体一致,也证实了本设计提出的算法是可行的,对梯形成形算法在FPGA上的应用研究具有一定参考价值。