# Effect of NO Post-Oxide-Annealing on TDDB Reliability of 4H-SiC MOS Oxidation

Caiping Wan<sup>1</sup>, Yingjie Wang<sup>2</sup>, Wenting Zhang<sup>3</sup>, Shihai Wang<sup>1</sup>, Qinpei Zhou<sup>1</sup>, Hengyu Xu<sup>1</sup>

Email: wancaiping@ime.ac.cn

Received: Jun. 9<sup>th</sup>, 2018; accepted: Jun. 21<sup>st</sup>, 2018; published: Jun. 28<sup>th</sup>, 2018

#### **Abstract**

Silicon carbide (SiC) devices have great potential in high voltage and high power applications as its unique physical and chemical properties. However, due to the presence of carbon, gate oxide reliability of SiC MOS devices has always restricted the development of SiC MOSFET (Mental-Oxide-Semiconductor Field-Effect Transistor) devices. The reliability of gate oxide is the key factors affecting the performance and reliability of SiC MOSFET. How to improve TDDB reliability of SiC MOS devices requires in-depth system research. Post-Oxide-Annealing (POA) in nitrogen-containing atmosphere is one of the most effective ways to improve the reliability of SiC MOS; it is based on a large number of post-oxide-annealing process research. The paper systematically studied the temperature of NO post-oxidation-annealing effects on 4H-SiC MOS TDDB (Time-dependent dielectric breakdown) reliability. The NO POA experiments is oxide in 1350°C before annealing at different temperature. The temperature of NO post-oxide-annealing is from 1200°C to 1300°C. The influence of oxide post-oxidation annealing process on gate oxide reliability of SiC MOS devices is compared and summarized by TDDB. The experimental results show that with the increase of annealing temperature, the lifetime of gate oxide layer gradually increases, but the equality decreases as well.

# **Keywords**

4H-SiC, SiC MOS Capacitors, Post-Oxide-Annealing, TDDB, NO

# NO退火对4H-SiC MOS器件栅氧化层 TDDB可靠性的影响

万彩萍<sup>1</sup>, 王影杰<sup>2</sup>, 张文婷<sup>3</sup>, 王世海<sup>1</sup>, 周钦佩<sup>1</sup>, 许恒宇<sup>1</sup>

1中国科学院微电子研究所,北京

文章引用: 万彩萍, 王影杰, 张文婷, 王世海, 周钦佩, 许恒宇. NO 退火对 4H-SiC MOS 器件栅氧化层 TDDB 可靠性的影响[J]. 智能电网, 2018, 8(3): 279-287. DOI: 10.12677/sg.2018.83032

<sup>&</sup>lt;sup>1</sup>Institute of Microelectronics, Chinese Academy of Sciences, Beijing

<sup>&</sup>lt;sup>2</sup>North China University of Technology, Beijing

<sup>&</sup>lt;sup>3</sup>State Key Laboratory of Advanced Power Transmission Technology, Global Energy Interconnection Research Institute Co., Beijing

2北方工业大学,北京

<sup>3</sup>全球能源互联网研究院有限公司,先进输电技术国家重点实验室,北京 Email: wancaiping@ime.ac.cn

收稿日期: 2018年6月9日; 录用日期: 2018年6月21日; 发布日期: 2018年6月28日

# 摘 要

碳化硅(SiC)材料因其独特的物理和化学特性,使得SiC器件在高压大功率领域具有巨大的潜力,但是由于碳元素的存在,SiC MOS器件的栅氧化层可靠性问题一直制约SiC MOSFET器件的发展,影响SiC MOSFET器件性能和可靠性的关键因素。如何提升SiC MOS器件的TDDB可靠性,需要展开系统深入的研究。基于大量的氧化后退火工艺研究基础,氧化后在含氮氛围内退火是较为有效的手段之一,本论文系统研究NO氧化后退火工艺中温度对于4H-SiC MOS器件栅氧化层TDDB (Time-dependent dielectric breakdown:时间相关介质击穿)可靠性的影响,通过将1350℃干氧氧化后的样品的进行不同温度的一氧化氮(NO)氧化后退火,通过TDDB对比总结氧化后退火工艺对SiC MOS器件栅氧TDDB可靠性的影响,实验结果表明,随着退火温度的增加,栅氧化层寿命逐渐增加,但是均一性却逐渐降低。

# 关键词

4H-SiC, SiC MOS电容,氧化后退火,TDDB,NO

Copyright © 2018 by authors and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY).

http://creativecommons.org/licenses/by/4.0/

Open Access

# 1. 引言

宽禁带半导体由于近年来在材料生长和器件技术方面的突破,成为超越硅基器件的先进功率器件的候选者,在宽禁带半导体中,由于大直径晶圆的可用性,SiC 材料在高电压和高电流电网和轨道交通等领域尤其具有吸引力[1]。由于对于电源转换需求的不断增长,基于 SiC 的金属氧化物半导体场效应晶体管(MOSFET)作为高性能功率开关器件受到了很多关注,如在电源、电动机控制、电动混合动力汽车和电力传输等方面[2]。

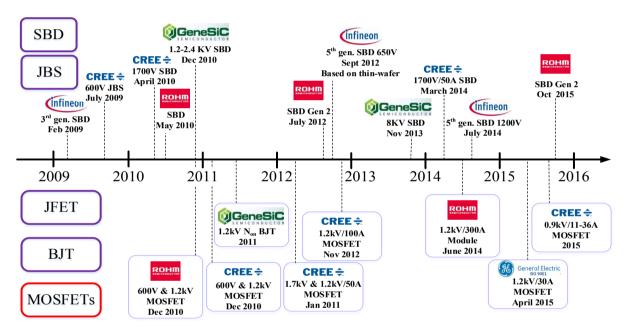

相比于传统硅(Si)材料,碳化硅(SiC)因其更宽的禁带宽度(3.26 eV)、更高的热导率和更高的临界击穿场强,在大功率开关电路和电力系统应用领域得到了广泛的关注。其中功率器件最突出的性能优势在于其高压、高频和高温工作特性,可有效地降低电力电子系统的功率损耗[3]。目前,国际上多数行业领先的半导体器件厂商,已在 SiC MOSFET 器件产品化道路上取得了巨大进展。现阶段,商用 SiC MOSFET 产品绝大多数为 N 沟道平面垂直结构,且多家公司已推出了更新的 SiC MOSFET 产品,其应用前景被寄予了很大希望。虽然目前,SiC MOSFET 已经在功率市场上推出产品,但是 SiC 材料由于 C 元素的存在,导致 SiC MOSFET 的 SiO<sub>2</sub>/SiC 界面处存在大量的界面态,约比 Si MOSFET 高出 2~3 个数量级[4],导致 SiC MOSFET 的沟道迁移率低,氧化物可靠性差,阈值电压存在漂移等,相对于二极管器件,SiC MOSFET 器件的发展仍然缓慢[5][6],图 1 所示的是碳化硅电力电子器件的发展现状。

SiC 材料的本征载流子浓度仅为 1.5E-9 cm<sup>-3</sup>, 比硅(Si)材料的本征载流子浓度低 19 个数量级。故此,

SiC 器件在出厂检测或者早期使用过程中,有一些缺陷无法和传统硅器件一样使用漏电流等指标参数进行筛选、隐藏的缺陷难以被激发和发现,给样品的早期失效筛选带来极大困难。通过结合 SiC 器件的电学特性分析进行早期器件工艺过程管控和工艺改善,尤其是完善核心关键工艺的研究,对于提升器件早期筛选和排查可靠性隐患尤为重要,栅氧工艺作为 SiC MOS 器件的核心工艺备受关注。

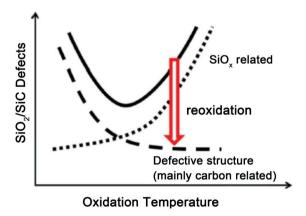

SiC 材料在氧化过程中,氧化温度过高或者过低会导致栅氧材料中存在氧空位和 C 残留,因此,在 SiC 外延材料上获得界面特性优良的  $SiO_2$  介质,需要对氧化工艺进行特别的优化,如进行超高温栅氧工 艺或者氧化后退火工艺等。目前普遍认为 C 相关的缺陷是导致  $SiO_2/SiC$  界面缺陷密度较高的主要原因,相关研究表明,在高温氧化后,SiC MOS 器件的界面特性仍有较大的提升空间(图 2 所示),可以通过氧化后退火(POA)工艺进一步改善[5]。

本论文主要研究氧化后 NO 退火工艺对  $SiC/SiO_2$  界面和栅氧可靠性的影响,借助于 TDDB 的分析来 考量栅介质的可靠性。

Figure 1. The current development of SiC power electronic devices 图 1. 碳化硅电力电子器件发展现状

Figure 2. Improvement of gate oxide after reoxidation ② 2. 氧化后退火工艺对于栅氧质量的改善效果

# 2. 实验与测试分析

相比于 Si, SiC 的氧化过由于 C 元素的存在, 更为复杂, 目前 SiC 的氧化过程通常是在干氧环境中进行, 氧化过程是氧气的扩散与 CO 释放的过程, 理想的反应方程式如公式(1)所示[7] [8]:

$$\operatorname{SiC} + \frac{3}{2} O_2 = \operatorname{SiO}_2 + \operatorname{CO} \tag{1}$$

但是在实际氧化过程中,当氧化温度过低时,SiC 与  $O_2$  会发生反应不充分的现象,导致界面处的 C 残留,如公式(2)所示:

$$SiC + O_2 \rightarrow SiO_2 + C(s) \tag{2}$$

当氧化温度过高时, Si 元素与 O 元素无法生成紧密的氧化物, 生成 SiO, 使得界面处产生氧空位

$$SiC + O_2 \rightarrow SiO(g) + CO(g)$$

(3)

在实际氧化过程中,氧化温度过高或者过低产生的氧空位或者碳残留都会产生界面质量问题,导致栅氧可靠性偏低。目前报道显示高温氧化后退火对于改善栅氧质量效果显著,关于 SiC MOS 的氧化后退火工艺,无论是科研界还是工业界,目前主要采用的依然是氮化工艺,即在氧化以后在含有氮的氛围中退火。在氮化过程中,扩散到界面处的 N 原子,可以分解界面处的碳簇,减小碳团簇的尺寸,从而有力消除界面处的碳,降低界面态密度。氧化后退火主要采用一氧化二氮( $N_2O$ )、一氧化氮(NO)、混合气体(FGA)、NO&FGA 气体等[9],据报道目前效果最容易且效果最好的为 NO 退火。NO 退火可以减少界面处 C 团簇的存在,形成 CO 或者与 C=N 和 Si=N 提升界面处的栅氧可靠性[10]。本文主要研究氧化后不同 NO 退火条件(不同温度)对于栅氧化层 TDDB 可靠性的影响

# 2.1. 实验

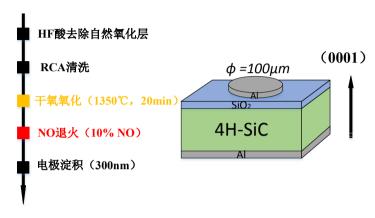

本次实验研究的是 NO 退火对 SiC/SiO<sub>2</sub> 界面和栅氧可靠性的影响,主要研究高温氧化后 NO 退火温度和时间对栅介质 TDDB 可靠性的影响。实验采用的高温干氧氧化后的氧化后退火工艺,实验样品是在 4 英寸的 4H-SiC 晶圆的 Si 面上进行的,衬底厚度为 350 um,外延层厚度为 12 um,外延掺杂浓度为  $8 \times 10^{15}$  cm<sup>-3</sup>,后样品在 HF 酸溶液中清洗以去除自然氧化层,然后在 1 atm 的干氧氧化氛围中进行 1350  $\mathbb C$ 的干氧氧化以形成 50 nm 左右厚度的氧化层,氧化时间约为 20 min,而后在 10%NO 氛围中进行氧化后退火(POA),最后在正面淀积一层 200 nm 厚直径为 300 um 的正面电极,背面淀积一层 Al 电极,样品制作流程如图 3 所示,相关样品的详细实验信息如表 1 所示。

## 2.2. 测试与分析

栅氧介质的完整性可靠性由 TZDB(time-zero dielectric breakdown)和 TDDB(time-dependent dielectric breakdown)确定,它通过大量实测击穿电荷量  $Q_{BD}$ 、击穿时间  $t_{BD}$ 等大量数据的统计分布来表征氧化膜的质量,并可通过它来预测栅氧化层的寿命。根据实验时 MOS 上外加电场的方式,常用的 TDDB 寿命评价方法主要采用 TDDB 和 TZDB 零时介质击穿(Time-zero dependent breakdown)。

#### 2.2.1. TZDB 测试

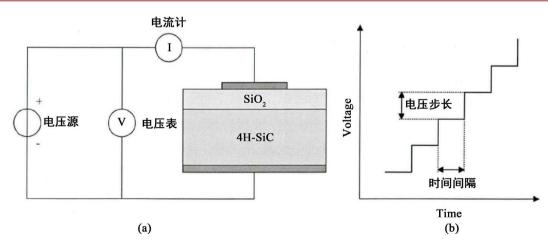

TZDB 测试是在栅氧化层上施加从零伏开始随时间线性增加的电压。实验过程可能会记录了上千个数据,可在较短时间内获得栅氧化层击穿过程的详尽信息。在本论文测试过程中,先进行 TZDB 测试,然后根据测试图像,确定击穿电压,TZDB 测试原理图如图 4(a)所示。设置半导体特征分析仪对 SiC MOS 样品施加直流电压,施加电压的波形如图 4(b)所示。其中电压的范围设置为 0~70 V,步进为 0.5 V,每次

测量时间间隔为 1 s。当参数设置完毕后选样品直径为 100  $\mu$ m 栅电极并将一探针与栅电极接触,另一探针与背面金属接触。通过 TZDB 的测试可以估算出 SiC MOS 的氧化物的击穿场强  $E_{BD}$ ,击穿场强可由公式(4)得到:

$$E_{BD} = \frac{V_g - V_{FB}}{E_{OT}} \tag{4}$$

## 2.2.2. TDDB 测试

TDDB 测试根据 TZDB 测试的结果,以稍小于击穿电压的电压进行测试,得出击穿时间并进行分析,

**Figure 3.** Process experimental procedures and sample information **图 3.**工艺实验步骤及样品信息

Table 1. Information of samples and the experiment conditions 表 1. 样品信息及实验条件

| 样品编号 | 氧化条件               | 氧化后退火条件              |

|------|--------------------|----------------------|

| A    | 干氧氧化,1350℃, 20 min | 未退火处理                |

| В    |                    | NO 退火: 1300℃, 30 min |

| С    |                    | NO 退火: 1250℃, 30 min |

| D    |                    | NO 退火: 1200℃, 30 min |

Figure 4. (a) TZDB Test Schematic; (b) Applied Voltage Waveform **图** 4. (a) TZDB 测试原理图; (b)施加电压波形

用于测试栅氧化膜在此电压下的寿命,TDDB 测试是在栅极施加低于栅氧化层本征击穿场强,本身并不足以引起本征击穿,但由于施加电应力过程中,氧化层存在缺陷的缘故,经历一定时间后,电荷在缺陷附近聚集或者缺陷捕获电荷而发生的击穿。与时间有关的栅氧介质击穿是影响 SiC MOS 可靠性的主要因素。一般说来,击穿是由于氧化硅中电场过高、电流过大,从而造成电荷累积引起的。氧化层的击穿过程,目前认为分为两个阶段,即建立(磨损)阶段和击穿阶段。在建立(磨损)阶段,氧化层内部及 SiC/SiO2 在电应力的作用下,发生缺陷的积累,当积累的缺陷达到某一程度后,局部区域的缺陷数达到某一临界值,转入击穿阶段[11] [12] [13] [14]。在击穿阶段,在热、电正反馈作用下,氧化层迅速击穿。因此,栅氧化层 TDDB 测试的寿命由建立(磨损)阶段所决定。栅氧化层内部及 SiC/SiO2 在 TDDB 测试过程中发生缺陷的积累,当某一局部区域的缺陷数达到某一临界值,触发局部电流密度上升,即发生击穿。通常,栅氧化层可以被认为有很多个这样小的局部区域并联组成,只要有一个局部区域发生击穿,整个氧化层就发生击穿记录  $T_{BD}$ 。因此,TDDB 测试的寿命数据一般用 Weibull 分布来描述[13] [14]。

通常用累计失效率来评估 MOS 器件栅氧的可靠性,累积失效概率也称不可靠度,与可靠度相对,指的是产品在规定的条件下在时间 t 以前失效的概率,也就是栅氧化层在规定的条件下在时间 t 及 t 以前失效的概率,即寿命这一随机变量( $T \le t$ )的分布函数,通常记为 F(t):

$$F(t) = P\{T \le t\} = 1 - R(t) \tag{5}$$

式中 T 为随机变量,这里指产品的寿命,在本轮文中指器件栅氧化层的寿命,在实际数据处理中,累积失效率 F(t)近似值为:

$$F(t) = \frac{n(t)}{N} \tag{6}$$

式中 N 为进行实验的实验统计样品总数,n(t)为实验到 t 时刻失效的样品总个数。一般选取累计失效率为 63.2%时的测试参数作为比较时所用的典型参数[15],是因为绝大部分器件的失效击穿时间都处在累计失效率为 63.2%击穿时间附近。累计失效率为 63.2%时的  $Q_{BD}$  测试参数不受前期失效的影响,与累计失效率为 100%时的测试参数接近,偶然性也小。

#### 2.2.3. 栅氧可靠性击穿统计分布

在统计分立器件的栅氧的栅氧化层击穿 TDDB 试验中通常使用  $Q_{BD}$  的 Weibull 分布进行统计分布分析,Weibull 分布能够将器件的累积失效概率 F(t)与器件可靠性寿命 t 紧密关联,其公式如下[15]:

$$F(t) = 1 - e^{-\left(\frac{t}{\eta}\right)\beta} \tag{7}$$

$\eta$  是特征寿命,表示当有 63.2%的器件失效时所对应的时间[15]。 $\beta$ 是威布尔分布的斜率因,也称为威布尔斜率,是标定威布尔分布的形状因子,一般累计失效率也用以下公式表示:

$$F = 1 - \exp(-AD) \tag{8}$$

式中 A 表示面积,D 为缺陷密度,一般在低场下的击穿是由于氧化物缺陷引起的,而在高场下一般是由于本征缺陷引起的击穿,对公式(8)两边取对数可得:

$$-\ln(1-F) = AD \tag{9}$$

公式(9)和公式(8)转换可得到:

$$\ln\left[-\ln\left(1-F\left(t\right)\right)\right] = \ln\left(AD\right) = \beta \ln\left(\frac{t}{\eta}\right) \tag{10}$$

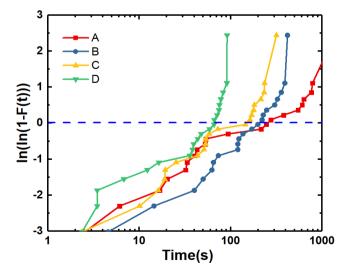

若以  $\ln\left[-\ln\left(1-F(t)\right)\right]$  为纵坐标,以  $\ln t$  为横坐标,就会得到一条以 $\beta$ 为斜率的直线,在 Weibull 分布中的 $\beta$ 值是可靠性评估中非常重要的参数, $\beta$ 值越大,器件失效越快。

# 2.3. 结果与讨论

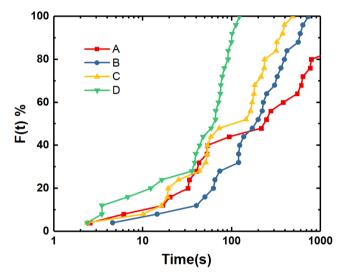

根据 I-V 曲线的结果,4 个样品栅氧化膜的击穿场强  $E_{BD}$  均达到了比较高的水平,击穿时的电场强度基本相同。A、B、C、D 样品的击穿场强分别为 10.05 MV/cm、9.66 MV/cm、9.70 MV/cm、9.62 MV/cm。在 TDDB 实验过程中,对样品施加略低于击穿电压的电压,在此次失效统计过程中,所施加的电压为 51V,对于每一个直径为 100  $\mu$ m 样品点都重复施加恒压 TDDB 测试,然后记录每个样品点击穿的时间,统计每个样品的累积失效分布曲线,如图 5 所示。

通常取失效率在 63.2%时的应力时间为器件的平均寿命。故由图 6 总结得出样品 A、B、C、D 克的平均寿命如表 2 所示。

**Figure 5.** The summary of cumulative failure rate distribution curve **图 5.** 累积失效率分布曲线汇总

Figure 6. The Weibull distribution curve 图 6. Weibull 分布曲线

Table 2. The average lifetime of the NO POA samples 表 2. NO POA 样品平均寿命

| 样品编号 | 施加电压(V) | 平均寿命(s) |

|------|---------|---------|

| A    | 51V     | 440     |

| В    |         | 330     |

| С    |         | 210     |

| D    |         | 68      |

4H-SiC MOS 器件栅氧化膜的质量还可以从击穿时氧化膜所承受的电场强度和击穿时间来判断,从图 6 中可以看出各个样品的斜率对比: D > C > B > A,可以看出,经过高温 10%NO 退火工艺处理的样品的直线斜率明显要比未处理的样品要大,比未处理的样品曲线要陡峭。经过处理之后的样品,尤其是经过 1200℃ 10%NO 退火 30 min 处理的样品,与未处理的样品形成了明显对比。这个现象从另一个方面证明,高温 NO 退火处理能够让 4H-SiC MOS 栅氧化膜质量变得均一,即样品击穿时间点的数据分布较为紧密,即样品从第一个击穿到最后一个击穿,击穿电荷量的差别并不是特别大。

# 3. 结论

栅氧化层的 TDDB 是一项非常重要的可靠性特性。文章考察了高温 NO 退火处理对于 4H-SiC M0S 栅氧化膜质量的改善作用。首先通过 I-V 测试对氧化膜的质量进行了评价,通过实验得出 4H-SiC MOS 样品的击穿场强 E<sub>BD</sub> 以及 MOS 栅氧化膜与 SiC 衬底之间的势垒高度这两个重要参数来判断高温 NO 退火处理对氧化膜质量的改善作用。

其次重点从 4H-SiC MOS 样品高温 NO 退火处理对 SiC MOS 栅氧化膜 TDDB 特性的影响 TDDB 行为方面对氧化膜质量的改善做出评价。通过恒压 TDDB 测试方法得出击穿时间,计算得累积失效率和 Weibull 参数值。并画出栅氧化层的失效率同击穿时间的关系和 TDDB 击穿时间的 Weibull 统计分布对栅氧化膜 TDDB 行为进行了评价。得出的结论如下:

- 1) 高温 NO 退火处理能够有效提高样品的均一性,增加本证击穿的比率,并且能够有效去除早期击穿的样品点。

- 2) 随退火温度的降低,栅氧化层寿命逐渐降低,但根据 Weibull 分布曲线的斜率来分析,样品可靠度,均一性却逐渐提升了。

# 致 谢

感谢北方工业大学硕士研究生王影杰同学对于测试工作的支持,同时感谢中国科学院微电子研究所 高频高压中心相关老师对于流片和测试分析工作的指导。

# 基金项目

国家电网公司总部科技项目-(5455DW150006)。

# 参考文献

- [1] Kimoto, T. and Yonezawa, Y. (2017) Current Status and Perspectives of Ultrahigh-Voltage SiC Power Devices. *Materials Science in Semiconductor Processing*.

- [2] Tsuchida, H., Kamata, I., Miyazawa, T., Ito, M., Zhang, X. and Nagano, M. (2017) Recent Advances in 4H-SiC Epitaxy for High-Voltage Power Devices. *Materials Science in Semiconductor Processing*.

- [3] 唐亚超. 4H-SiC MOSFET 关键工艺开发与器件制作[M]. 成都: 电子科技大学, 2016.

- [4] Fiorenza, P., Vivona, M., Iucolano, F., Severino, A., Lorenti, S., Nicotra, G. and Roccaforte, F. (2017) Temperature-Dependent Fowler-Nordheim Electron Barrier Height in SiO<sub>2</sub>/4H-SiC MOS Capacitors. *Materials Science in Semiconductor Processing*.

- [5] 王弋宇. 介质/SiC 界面研究和 MOSFET 器件研制[D]: [博士学位论文]. 北京: 中国科学院大学, 2015.

- [6] Power SiC 2016: Materials, Devices, Modules, and Applications. http://www.i-micronews.com/category-listing/product/power-sic-2016-materials-devices-modules-and-applications.html

- [7] Kita, K., Kikuchi, R.H., Hirai, H. and Fujino, Y. (2014) Control of 4H-SiC (0001) Thermal Oxidation Process for Reduction of Interface State Density. ECS Transactions, 64, 23-28. https://doi.org/10.1149/06408.0023ecst

- [8] Song, Y. and Smith, F.W. (2002) Phase Diagram for the Interaction of Oxygen with SiC. Applied Physics Letters, 81, 3061-3063. https://doi.org/10.1063/1.1514397

- [9] 王弋宇, 彭朝阳, 申华军, 李诚瞻, 吴佳, 唐亚超, 刘新宇. Characterization of the Effects of Nitrogen and Hydrogen Passivation on SiO<sub>2</sub>/4H-SiC Interface by Low Temperature Conductance Measurements. 半导体学报: 英文版, 2016(2): 148-154.

- [10] Zhao, P., et al. (2006) Investigation of 4H-SiC MOS Capacitors Annealed in Diluted N<sub>2</sub>O at Different Temperatures. Microelectronic Engineering, 83, 61-64. <a href="https://doi.org/10.1016/j.mee.2005.10.026">https://doi.org/10.1016/j.mee.2005.10.026</a>

- [11] 张平. MOS 器件界面态特性研究及其可靠性分析[D]: [硕士学位论文]. 广州: 暨南大学, 2015.

- [12] 廖翠萍. 超薄栅氧化层的 TDDB 特性与寿命评估[D]: [硕士学位论文]. 西安: 西安电子科技大学, 2007.

- [13] 汤斌. 氮等离子体处理对 SiCMOS 栅氧化膜 TDDB 特性的影响[D]: [硕士学位论文]. 大连: 大连理工大学, 2015.

- [14] 冯军宏. 氮离子注入对栅氧化层 TDDB 可靠性的影响[D]: [硕士学位论文]. 上海: 复旦大学, 2011.

- [15] 施罗德, 爱民. 半导体材料与器件表征技术[M]. 大连: 大连理工大学出版社, 2008.

# 知网检索的两种方式:

- 1. 打开知网页面 <a href="http://kns.cnki.net/kns/brief/result.aspx?dbPrefix=WWJD">http://kns.cnki.net/kns/brief/result.aspx?dbPrefix=WWJD</a> 下拉列表框选择: [ISSN], 输入期刊 ISSN: 2161-8763,即可查询

- 2. 打开知网首页 <a href="http://cnki.net/">http://cnki.net/</a> 左侧 "国际文献总库"进入,输入文章标题,即可查询

投稿请点击: <a href="http://www.hanspub.org/Submission.aspx">http://www.hanspub.org/Submission.aspx</a>

期刊邮箱: sg@hanspub.org