# A Fully Synthesizable Design Flow for High-Speed Dual-Phase Domino Logic

#### Yu-Tzn Tsai, Hsiang-Hui Huang, Ching-Hua Cheng

Department of Electrical Engineering, Feng-Chia University, Taichung Email: chengch@fcu.edu.tw

Received: Apr. 1st, 2013; revised: Apr. 22nd, 2013; accepted: May 3rd, 2013

Copyright © 2013 Yu-Tzn Tsai et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Abstract: Domino logic design offers smaller area and higher speed than complementary CMOS design. Domino logic design has become a very popular technology used to design high-performance processors. There have been several studies conducted on dual phase operation dynamic circuit, but most have focused on theory without practical implementation in large circuits. In this thesis, we establish the cell based synthesis design flow of the high speed dual phase operation dynamic circuit, which includes skew tolerant, low-power and high-performance characteristics. There are three major contributions of this work. First, a high-performance dual phase circuit design technique is proposed. Second, a supported synthesizable design CAD flow is established. The skew-tolerant issue is also considered in the tools. A domino cell library with two noise-alleviation (charge sharing and crosstalk) capabilities is generated to support the cell-based synthesis CAD design tools. Third, the built-in performance adjusting mechanism is conducted within the design. This mechanism can support turning performance after chip fabrication. The test chip of dual-phase 32 × 32 high-speed multiplier with performance mechanism was successfully validated.

**Keywords:** Dual-Phase Dynamic Circuit; Pipeline Dynamic Circuit

## 高速双相动态电路暨设计自动化流程之实现

蔡佑慈, 黄翔晖, 郑经华

逢甲大学电子工程学系,台中 Email: chengch@fcu.edu.tw

收稿日期: 2013年4月1日; 修回日期: 2013年4月22日; 录用日期: 2013年5月3日

摘 要:由于骨牌逻辑电路通常较互补式金氧半组件电路计具有较小的面积与更快的速度,所以已经被广泛使用于设计高速电路如微处理器的设计中。虽然有许多关于动态电路的研究,然而大部份的研究却忽略探讨如何实现其研究成果。在本论文中,我们设计了一个创新的双相操作高速动态电路,它具有管线式(pipeline)的电路结构,运作速度不受电路复杂度的影响,使得它的效能较传统动态电路的提升极多,因具容忍频率歪斜(skew tolerant)的特性,可使用标准组件之设计流程来设计。最后,芯片测量结果证明完成了下述设计目标:一个Performance Scalable 的 very high speed dynamic 32 × 32 bits 之 multiplier 具有下列特性: 1)高速频率操作,工作效能较一般传统动态电路改善甚多。2)可以为容忍 clock skew,使用 Duty Cycle Pulse Generator (DCPG)的技术来产生 double clocking 的时间,可借由 DCPG 来克服 process variation 及 cell based design clock tree routing 所造成的 skew 的问题。3)使用 BIST 技术作为正常效能的自测功能,此功能可转为本芯片在 process 后仍可以调整电路效能,做为电路 performance management 的机制。

关键词:双相动态电路;管线式动态电路

## 1. 简介

### 传统动态电路

经由自行研究发展并合成出来的动态电路与一般传统的静态电路比较可以发现到,以平均值来看的话,动态电路的效能比传统的静态电路增加了30%。

经由我们深入分析后发现,电路的效能其实和电路中晶体管的数量是有关系的,经我们所合成出来的动态电路与一般传统的静态电路晶体管个数的比较表,相较先前效能低于平均值的各个电路 c17、c432、c3540、c6288,它们晶体管数增加的数量也都是高于平均值(70.32%)的,结论是电路在经过 Bubble push 之后,晶体管的数目会增加,增加的程度会因各个电路的不同而有所不同,但所增加的晶体管数目愈多,所损失的效能也是成正比的增加的。

上述全正向动态电路合成流程中包含 Bubble push and logic optimization 两项最重要工作<sup>[1-6]</sup>。此 flow 看似正确, 但里面确隐藏了一些使电路的面积变大, 而导致效能变差的原因: 1) 在 Bubble push 前的 decomposition: 此动作为拆解电路中连结逻辑闸 AO、 OA gate,这个动作将原本优化完的电路完全的破坏 掉,而又拆建成了单纯的 AND 和 OR 的 function,所 以不管前面这个电路在 Synopsys 合成中优化的多好, 到了这一个步骤又被还原成了原本电路未优化前的 状态,以致就算被优化化简完的电路到了此一步骤 后, 电路的面积又会再次的胀大。2) 在 Bubble push 后的 Synopsys 无法优化: 电路经由 Bobble push 后产 生的 internal gates (positive framework), 它是一个没有 包含负向逻辑的电路,而 Synopsys 的 design compiler 这个商用 CAD tool 没有办法做使用全正相逻辑的电 路优化,也就是说,这个电路如果再送到 design compiler 这个商用 CAD tool 去做逻辑电路优化,而出 来优化完成后的电路又会将负向的逻辑给 mapping 进 去,而没办法给动态电路使用。

我们的目标是希望电路操作速度越快越好,改进单相动态电路的缺点,采用双相动态电路(DP domino),在本论文中,我们针对高速双相动态电路技术,去建立一个使用标准组件的自动化设计流程(Cell-Based Design Flow),在这方面,我们使用自行研发的程序结合现行的 EDA 工具来自动合成电路并且完成

芯片的实作与验证。这个芯片上达成了三项成果:一、 我们实证了一个双相操作动态的高效能电路设计技 术,该设计使用闩锁型的动态电路组件库,它具有处 理电荷分享(Charge Sharing)与串音干扰(Cross-Talk) 等噪声减轻问题(Noise-Alleviation)的能力。二、一个 支持双相动态电路自动电路合成的自动化设计流程。 三、除了高速双相动态电路的设计与合成技术外,此 颗芯片内设有 Built in self test (BIST)技术辅助芯片于 高速工作时的自测功能。我们利用这个自测功能可以 "逼出"这个双相动态电路的最高工作频率,我们是 使用 DCPG 的频率周期可调整电路技术,借由这个技 术来调整电路的效能。简单说明如下, DCPG 可以调 整慢速的系统 clock 频率去产生待测电路所需要的高 频率频率讯号,不需依靠调整全数字锁向回路电路 (All-Digital Phase Loop, ADPLL)来改变频率,因此影 响电路效能的范围较小,可以在输入的 4 MHz 或 500 KHz 频率下透过 ADPLL 后再将频率调整至稳定的 666 MHz。这个BIST 机制除利用 DCPG 来做频率 Duty cycle 的调整,来产生预期的频率周期协助验证高速双 相动态电路的效能外, 并配合供应给该高速双相动态 电路的 Input patterns 是采用线性回授移位缓存器 (LFSR)产生随机式向量(Random Test Pattern),再藉由 输出结果分析(ORA),以确定高速双相动态电路的正 确功能与最高工作速度。

## 2. 双相动态电路架构设计与合成

#### 2.1. 电路架构

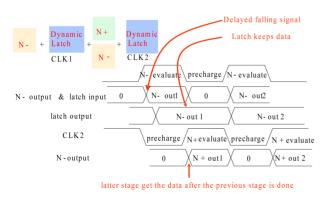

不管哪种 type: N+、N-,它有一定的接法(N- type 的 cell 无法与其它任何 type 的 cell 相接),否则会发生 Internal racing。为了避免这个错误发生,我们插入了一个 dynamic latch 在 N- type cell 的后方,此时第一级 N- type cell 的 output 的值会被 dynamic latch 保存半周期,而在第二级我们将 clk 延后半周期去取值 (evaluate),这样一来,即使第一级 N- type cell 在 evaluation phase 还没稳定而有个 falling 的讯号时,也不会对第二级 N- or N+ type cell 造成 internal race 的情况发生,因为第二级 N- or N+ type cell 的 input 是经 dynamic latch 延后半周期的稳定输出。

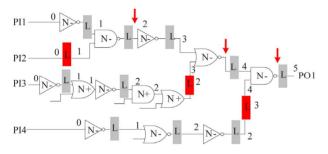

我们的电路具有 clock skew tolerant 的能力,图 1 我们可以了解如果 clk2 与 clk1 有 clock skew 因为都含 在 latch output 的值保持时间中(N- out1 时间与 N+ evaluation 时间之 overlap 的区域),所以仍可维持function 正确。

### 2.2. 自动化合成流程

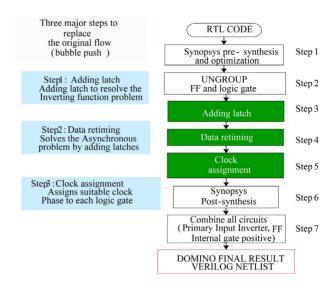

为了使电路容易合成使用我们所 proposed 的技术,所以提出了一个自动化设计流程。在我们的 flow中,将 Bubble push 这个动作给拿掉,这样一来不管是在 Bubble push前的 Decomposition或在 Bubble push后的 Synopsys 无法优化的两个原因就都不会存在。我们是利用两个 phase 的 clock 及 dynamic latch 来解决了这个问题,并用它来取代了原本的 Bubble push 这个动作。

部分流程如图 2 所示,会先将合成后电路做拆解动作将电路分成组合逻辑部分与 Flip-Flops (FFs)两个部分,接下来整个流程着重于处理组合逻辑部分。流程中的 add dynamic latch、data retiming 和 clock assignment 这三个步骤即为达到动态双相高速电路的实现的三个核心步骤,下面将会依序介绍这三个步骤。

Step1: 先将所设计的 RTL code (Verilog format) 在 *Synopsys* 做逻辑层次与闸层次优化,合成出形态为闸层次的 Verilog 电路。

Step2: 电路再进行 mapping 成动态电路时只能处理组合电路,因此在此步骤必须将组合电路从电路中独立出来,让后续的程序处理。

Step3: Add Dynamic Latch。利用 SIS 来完成,会将电路中有用到负向逻辑的晶体管加入 dynamic latch 以避免 internal racing。详细步骤如下:

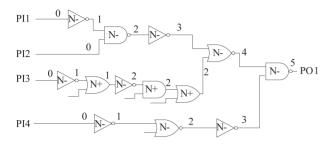

1) 首先,我们将对电路中每个节点做对应的 N+、N-gate 去做标号的动作。

Figure 1. Dynamic NAND2 after adding dynamic latch 图 1. NAND 闸与动态 latch 的组合

Figure 2. Automation design flow for DP domino circuit 图 2. DP domino 电路之设计流程

- 2) 把每个节点的从 input 到这个节点的 level 都标出来(当同一个 gate 有两种不同的 level 时,取最大的) 当遇到正向的 gate "N+"的时候 level 不用加 1,因为正向的 gate 接任何的电路都不会有 internal racing 的问题发生,而遇到负向的 gate "N-"时,level 加 1,如图 3。

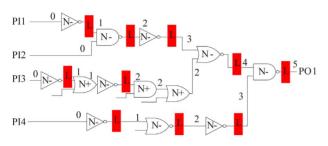

- 3) 搜寻每个节点,当此节点的 level 比它 fanin 节点的 level 大于 1 以上时,加上一个 dynamic latch 在此节点上,如图 4。

Step4: Data Retiming。解决因在电路的任意节点插 dynamic latch 所造成每笔数据到达时间不一样的问题。

- 1) 找出每个节点中,它 fanin 的 level 比它自己本身还要小两级以上的节点。

- 2) 找出这些节点后,将它的 fanin 加入 dynamic latch,此时需将找出节点的 level 与它的 fanin level 相比,如果大于 1 以上则必需在 fanin node 加 dynamic lath(差几个就要加几个),如图 5。

Step5: Clock Assignment.

加了 dynamic latch 后,再来就是 clock 要如何去 assign。clock assign 的方式是采用两个反向的 clock (phi0、phi1)分别供应给奇、偶数 level 的 logic gate,这样才可以保证每个 gate 都能在预定的时间到达,至此,dual phase high speed 的电路已完成,如图 6。

Step6: 在经过 latch insert、data retiming、及 clock assignment 后即可将先前因为无法处理循序电路而将

Copyright © 2013 Hanspub

Figure 3. Level assignment for gate level circuit 图 3. Add dynamic latch 前先将电路做分层标号

Figure 4. Add dynamic latch 图 4. 加入 dynamic latch

Figure 5. Data retiming 图 5. 资料时序重排

Figure 6. Latch insertion 图 6. Latch insertion 的示意图

FF 所切开部分再接回去现在 mapping 成为动态电路部分,整个 domino flow 才算完成。

#### 3. 测试芯片设计

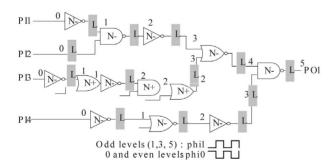

此芯片的内部电路架构主要分为三部分,如图 7。

Block 1: 产生高速的 clock 给 Block2 以及 CUT 使用。Block 2: 调整 Duty-cycle 频率之边缘,产生高速成法器需要的两个反向的 clock 信号(phi0、phi1)。Block 3: CUT。我们将高速的技术实现于高速乘法器,也就是验证本芯片的重点。外围是辅助验证高速乘法器的

电路: LFSR 产生随机数的 input patterns; MISR 是将 Multiply 运算后的 output 讯号做压缩以及比对; 而 en\_count 以及 count 还有其余的 logic gate 则是计数时间,控制 LFSR、MISR 的起始时间以及压缩时间。

#### 3.1. Block 1 之设计分析

为了可以产生待测电路(Block3)需要的高频率,则须依靠全数字锁向回路电路(ALL-Digital Phase Locked Loop, ADPLL),将输入的 4 MHz 频率调整至500 MHz。经由多任务器我们可切换 ADPLL 或是外部机台产生不同的频率给 Block2 使用。

#### 3.2. Block 2 之设计分析

经由模拟我们可以得知 Block3 最快可在 666.7 MHz下工作,而 ADPLL 虽可供应更高速度的 clock,但就稳定度来看,500 MHz 是最高也最稳定的速度,所以我们搭配 DCPG 来做频率 Duty cycle 的调整,产生我们预期的速度来协助验证 Block3 的高速双相动态电路设计。

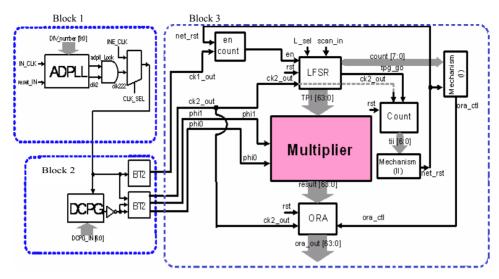

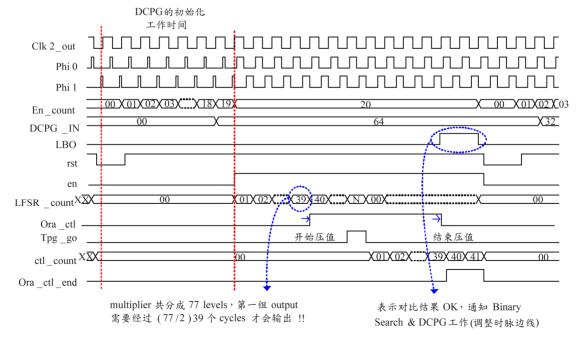

对数字控制脉冲波产生器(DCPG)输入一周期之脉波后,经由七位的控制讯号可产生 128 种输出变化。起始的控制讯号为 64,表示仍维持 50% Duty cycle 的频率,若电路欲工作更高的速度,可将控制讯号(DCPG\_IN[6:0])调整至 32(25% Duty cycle 的频率),也就是上个控制讯号的一半,若比对输出结果 LBO为 1,表示 clock 的速度还可再提升,需再调整控制讯号至 16(12.5% Duty cycle 的频率)继续观察;若比对结果 LBO为 0,表示 clock 的速度过高,需调整控制讯号至 48(37.5% Duty cycle 的频率)来降低速度。图 8为 DCPG 频率调变的规则是意图,利用这种方式"逼出"电路最高的工作速度。

由于 Block 3 的高速乘法器需要两个反向的 clock, 所以将 DCPG 的输出(phi0)经由 Buffer Tree 产生两组 clock, 利用 buffer delay 隔开两组 clock 时间, 形成反向频率, 使高速乘法器做 pipeline 工作。

Figure 7. The circuit structure for the testing chip 图 7. 测试芯片之内部电路架构

Figure 8. The frequency adjusting form using DCPG 图 8. DCPG 频率调变图

#### 3.3. Block 3 之设计分析

主要有三块电路,LFSR、Multiply、MISR。以下 是详细介绍:

此颗芯片內部电路的测试图样产生器(TPG)为输出 64 位的随机测式向量(Random Test Pattern)的线性回授移位战存器(LSFR),多项式为  $F(x) = 1 + X + X^{15}$ 。高速乘法器是这颗芯片的待测电路的核心,经由

高速双相动态电路设计流程自动合成,所以与其它 BIST module 搭配时需额外的时序控制。此 multiplier 被分为 76 层,观察结果时,需经过 38 个 clock cycle 才会出现第一组的 output pattern。

整个 BIST 机制电路中的输出结果分析器(ORA) 使用八个 MISR 电路来进行压缩工作。当 multiplier 的第一组 output pattern 产生时,压缩工作也随即进行,

Copyright © 2013 Hanspub

当压缩完最后一组 output pattern 后,将最后压缩完成的数值与 Golden 值比对,比对结果若相同,LBO = 1;反之,则 LBO = 0,由此可知待测电路的功能是否正确。由此方法我们便可知道电路的最高工作速度。

Mechanism(I)与 Mechanism(II)是由 logic gate 与 DFF 构成的电路,经由计数器的讯号脚位的逻辑讯号 启动。我们设定在特定的计数时间点(如 39,高速双相动态电路产生第一个 output 的周期数),将电路中数个逻辑讯号为 high 的脚位经由此两电路控制输出后,使 Q 为 high,做为下个 module 的制能。

图 9 为整颗芯片电路的控制时序示意图,将 4 MHz 的 clock 输入到 ADPLL,当 adpll\_lock 为 1 表示频率已稳定调整到 500 MHz,并将该频率的 clock 传送到 DCPG 作 clock 的频率调变。除了 ADPLL 产生的 500 MHz,我们可以藉由多任务器切换外部供应的 clock。当讯号送入 DCPG 后,需经过大约 20 个 clock 的初始化时间,才产生真正供应给待测电路的工作频率,此时 LFSR 的制能讯号启动,产生 patterns。当 LFSR 产生第 39 组 pattern 时,LFSR 的计数讯号脚位 count[7:0]启动 Mechanism(I)内部的 logic gate 与 DFF,使 ora\_ctl 为 1,通知 MISR 开始做压值(Data Compression);产生第 90 组 patterns(高速成法器运算的 pattern 数)时,借由 tpg\_go 讯号启动 Count 计数 38 组

时序,tii[6:0]的讯号脚位启动 Mechanism(II),使 net\_rst 为 0,通知 en\_count 终止 LFSR 工作;使 ora\_ctl 为 0,通知 MISR 停止压值,将最后压缩完成的数值 与 Golden 值比对,比对结果若相同,LBO = 1,表示电路的工作频率可能还可以再提高;反之,LBO = 0,这表示待测电路的工作频率过高,需将 DCPG\_IN[6:0] 的数值调整为 96,提升频率的 Duty cycle。

## 4. 芯片测试结果及分析

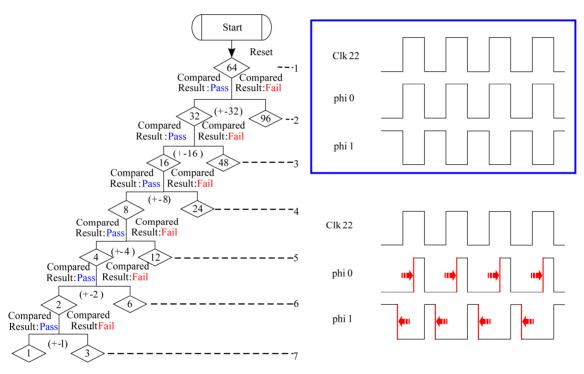

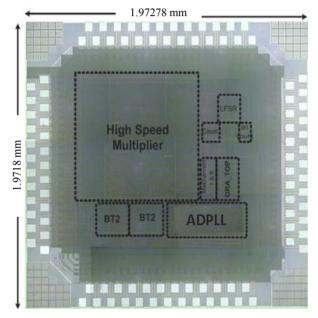

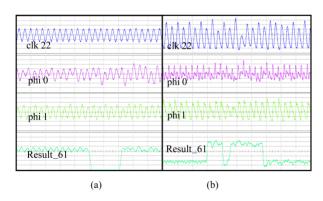

使用 TSMC 0.18u 制成所定的芯片照相图与规格 如图 10,量测芯片使用的仪器是逻辑分析仪(Logic Analyzer)与示波器(Oscilloscope),观察芯片在不同电压、不同速度的变化。图 11(a)为外部频率给 128 MHz,为 DCPG 没做 phi0 和 phi1 的微调的动作,(b)为内部频率给 128 MHz 和 DCPG 没做 phi0 和 phi1 的微调的动作。

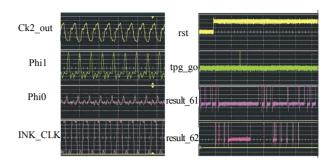

图 12 使用外部 clock 供应电路,而 phi0、phi1、ck2\_out 是经过 DCPG 但频率未调变后的结果以 result\_61 与 result\_62 为电路成功输出结果,而 tpg\_go 为控制 BIST 运作的信号。

## 5. 结论

在本论文中,设计了一个创新的双相操作高速动

Figure 9. The control timing diagram **图** 9. 控制时序示意图

| Technology                 | TSMC18 1P6M                         |

|----------------------------|-------------------------------------|

| Supply Voltage             | 1.8 v                               |

| Chip Size                  | $1.9718 \times 1.9727 \text{ mm}^2$ |

| Gate count                 | 95,138                              |

| External clock Frequency   | 128 MHz                             |

| External Power consumption | 203.3 mW                            |

| Internal clock Frequency   | 128 MHz                             |

| Internal Power consumption | 81 mW                               |

| Number of pins             | 100 CQFP                            |

Figure 10. Test chip photo and design specification 图 10. DP domino 芯片规格与照像图

Figure 11. Output frequency at 128 MHz 图 11. 频率为 128 MHz

Figure 12. The major output signals 图 12. 芯片主要输出波形

态电路,它具有管线式(pipeline)的电路结构,运作速度不受电路复杂度的影响,使得它的效能较传统动态电路的提升极多,因具容忍频率歪斜(skew tolerant)的特性,可使用标准组件之设计流程来设计,我们成功验证了 DP domino 电路的设计,并利用电路中的 BIST 电路来调整验证电路的最高工作速度。

## 参考文献 (References)

- M. R. Prasad, D. Kirkpatrick and R. K. Brayton. Domino logic synthesis and technology mapping. Workshop Notes, International Workshop on Logic and Synthesis, 1997.

- [2] T. Thorp, G. Yee and C. Sechen. Domino logic synthesis using complex static gates. 1998 IEEE/ACM International Conference on Digest of Technical Papers, San Jose, 8-12 November 1998: 242-247.

- [3] R. Puri, A. Bjorksten and T. E. Rosser. Logic optimization by output phase assignment in dynamic logic synthesis. 1996 IEEE/ACM International Conference on Digest of Technical Papers, San Jose, 10-14 November 1996: 2-8.

- [4] D. Harris, M. A.Horowitz. Skew-tolerant domino circuits. IEEE Journal of Solid-State Circuits, 1997, 32(11): 1702-1711.

- [5] R. Puri. Design issues in mixed static-domino circuit implementtations. Proceedings of International Conference on Computer Design: VLSI in Computers and Processors, Austin, 5-7 October 1998: 270-275.

- [6] G. Yee, C. Sechen. Clock-delayed domino for dynamic circuit design. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2000, 8(4): 425-430.