1. 引言

随着科学技术的发展,集成电路的结构日益复杂,步入SoC时代,在门级抽象层次上已经达到数以百万和千万门系统的设计和验证 [1]。为了保证设计的错误能及时发现,杜绝因重新设计和流片浪费开发成本和设计周期,就需要对电路进行正确性的验证。传统的模拟验证因其不完备性,已经不能适用于现时的较高抽象层次上的集成电路的验证,为了避免“20世纪60年代的软件危机”和“著名的奔腾FDIV错误”此类情况发生,促使人们去研究更完善的验证方法 [2] [3] [4]。

等价性验证是目前在实际的芯片设计中应用最广泛的形式化验证技术,如Synopsys公司的Formality,Mentor Graphics公司的FormalProTM,Cadence公司的Affirma等,并且能处理较大规模的设计 [5]。等价性验证一般采用图表示法和代数表示方法 [6]。图表示法主要使用二叉判定图(BDD),Brand利用BDD将电路建模为miter,计算所有可达状态这就是典型的基于有限状态机遍历算法 [7]。尽管最近十多年里,由于BDD方法的研究进展使得基于有限状态机遍历算法有了很大进步,但BDD需要大量储存和操作空间的问题仍无法避免,而且用布尔函数表示的状态集会成指数增长,存在状态空间爆炸问题。并且在抽象层较高的等价性验证中,受图形表示能力和图形构造上的制约,BDD无法胜任验证任务。相比而言,基于代数方法的等价性验证则更适合高层次验证。

代数学是数学的一个基本分支,它所处理和研究的数学对象是抽象的代数符号与概念,如整数、有理数、多项式、环、理想等 [8] [9]。其中多项式由于其描述电路时抽象建模能力强,表示具有规范性、无歧义性,使其成为理想的电路建模工具。Buchberger在1915年提出了多项式环上的Gröbner基,因其良序性方面的优势适用于计算机代数领域 [10] [11]。本文运用Gröbner基与乘法器电路结合的思想,在Galois域上采用迭代算法验证整数乘法器电路 [11] [12] [13] [14]。通过实验对比不同方法所需运行时间,易见各方法对乘法器等价性验证的效率影响。

2. Gröbner基理论

对于环R中给定的理想I,其Gröbner基一般并不唯一。这些Gröbner基与项序的选择密切相关,下面给出相关定义 [8] [9] [10]。

定义2.1 设 为任意一个域,变量序列

记为X,将含有n个变量的多项式环记为

或

。

多项式环中最重要的结构为理想,理想为多项式环中的一种子集,其中的元素对加法和乘法封闭。

定义2.2 多项式集合I 是环

的子集,如果满足

(1)

,

(2) 如果

,则

,

(3) 如果

,则

,

上述条件,则称I为多项式理想。

对于Gröbner基来说,多项式环

中单项式序的概念是一个基本概念,他可以定义出任意多项式的首项,从而保证多项式除法操作下余式唯一。

定义2.3 设

,集合Τ上的关系

称为一个单项式序,如果

满足下面条件:

(1)

为Τ上的一个全序;

(2)

,那么,

;

(3)

为Τ上的良序,即Τ上每一个非空子集有极小元。

其中

是所有单项的集合。

单项式序常见的有三种,字典序,分次字典序,分次逆字典序。

定义2.4 设

,如果

的最左边非空元素为正数,则称单项式

为字典序排序。

定义2.5 非零多项式

在给定的单项式序下,可唯一表示为

则称

为多项式f的首项系数,

为多项式f的次数,

为多项式f的首单项式,

为多项式f的首项。

定义2.6 在多项式环

上给定一个单项式序,非零理想I的有限子集

,如果满足

称G为理想I的Gröbner基。

结合多元多项式除法,Gröbner基理论为理想成员问题提供了一个判定过程:给定一个多项式

和理想

。通过计算余数是否等于零,则可判定q是否为I中的元素。

3. 代数模型

Buchberger算法利用S-多项式去求多项式的Gröbner基,该算法的时间和空间复杂度是指数级的,在实际应用中是不可行的。因此本文直接将电路建模为Gröbner基多项式。

考虑一个具有l个布尔输入

和m个输出

的电路C。它的每个内部门由一个门变量

表示。接下来在相同的布尔输入

下,设电路C'有m个不同的输出

。与电路C中每个门(输出)类似,在电路C'中由门变量

表示。

门电路的逻辑门用多项式和信号作为布尔变量建模。其布尔变量之间的多项式关系是

(1)

每个逻辑门都是以门输入变量来描述门输出变量的方式来建模的。

每个多项式的一般形式是:

其中首项

是门的输出变量,尾部

是由门的输入变量组成的术语。根据这个多项式形式,模型的所有首项都是相对素的。电路是在布尔值范围内操作,因此,对于变量u,可得到关系式

。满足等式左侧的多项式编码形式称为域多项式F。

定义3.1 设

是满足(1)的对应多项式的电路C每个门的集合,并且多项式

和

称为输入域多项式,

。则

中生成的理想用

表示。

定义3.2设C是一个电路。一个多项式

被称为电路C的多项式电路约束(PCC),如果把

和结果值

带入多形式p得0。

定义3.3 电路C被称为乘法器,如果满足

是PCC。

本文针对于简单部分积生成的乘法器,其中部分积是指由两个电路输入通过与门产生的输出。为了从Gröbner基中消除带有部分积的这些多项式,把定义3.3中乘法器的规范改为推论3.1中规定的规范。

推论3.1 电路C是乘法器,如果满足

,其中

。

通过展开定义3.3中的和式,并在推论3.1中用

替代

,很容易地验证推论3.1的正确性。

乘法器的结构包括多个全加器及半加器,下面就以简单的全加器为例,给出理想成员问题判定过程:

例1:实现图1所示功能

的全加器电路。

根据(1),得图1的代数模型是

其中规范多项式为

,将多项式变量按电路的逆拓扑顺序

排序,在此序下,用规范多项式

归约代数模型

:

通过计算得余数为0,因此提取的代数模型为Gröbner基。为了更好的加快验证效率,下节将介绍Gröbner基的约化。

4. 加法器重写

通常情况,关于生成的Gröbner基归约规范,会导致中间约化结果中单项式的数量急剧增加,而影响验证效率 [9] [15]。因此我们利用加法器重写,以便更有效约化Gröbner基 [12]。

首先在乘法器的门级表示中识别全加器和半加法器,并将它们视为独立电路。然后应用变量消去,即用相应的加法器规范来代替全加器和半加法器内部门的所有多项式。这会使表示整个乘法器的Gröbner基更小、更紧凑,从而加快了归约过程。

定义4.1 一个电路C被称为全加器,如果满足

是PCC;相应地,一个电路 被称为半加器,如果满足

是PCC。其中

表示输出,

表示输入。

例2 给出简单全加器电路 相应的规范多项式:

那么H是

关于序

的Gröbner基。

为了消除内部变量

,直接将输出

表示为加法器输入

的多项式。下面就给出相关定义和定理,其中R表示环

和

表示环

[9]。

定义4.2 给定

,消去理想

是

的理想,定义

[9]。

定理4.1 设

为理想,

是J关于序

的Gröbner基。那么集合

是消去理想

的Gröbner基 [9]。

例1 (续) 为了消除变量

,从H中删除涉及这些变量的多项式是不可行的。因此我们根据定理4.1中给定的序,去计算第二个Gröbner基

。再从

中删除涉及

的多项式,得

.

由定理4.1,

是

的Gröbner基,则Gröbner 基就通过加法器重写得以化简。值得一提的是,对于本文研究的能完全分为全加器和半加法器的乘法器,可以约化首项是全加器或半加法器的和输出多项式,如

中多项式

就可以被首项是

的多项式约化。将其从Gröbner基中消除会带来进一步的改进,但Gröbner基消除该方法有失完备性。

5. 增量式等价性验证

本节引入了一种基于电路列式切片的增量验证将乘法器电路的整体Gröbner基划分为2n个更小的切片Gröbner基。将问题分解为更小的2n个子问题,逐个解决 [15] [16]。

定义5.1 设C和C'是两个电路,如果

是一个PCC (

),那么电路C和C'是等价的,记为

。

引理5.1

当且仅当

。

引理5.2 设C和C'是 两个电路,G和

是理想

和

关于序

的Gröbner基。设

是一个反向拓扑序,使得

属于

中。那么

是理想

关于

的Gröbner基。

本文中的增量式等价性验证技术,使用切片和切片Gröbner基的定义 [15]。对电路进行切片,进而进行增量式的等价性验证,由于电路

的和的规范可能是未知的,或者无法在Z上以规范和抽象形式表示,不能使用对给定规范执行理想成员的资格测试。因此将

和表示为多项式集,并将它们的Gröbner基组合成一个模型

。然后将问题转化为测试

和

关于

中变量之间的成员关系。

定义5.2 设是C和C'上述的两个电路

1) 对于每对输出位s和s',我们确定其输入锥,即与门,其依赖于:

2) 切片

定义为连续锥

的差:

若

是切片

中电路C和C'的门 的多项式集,则易证

是切片

的Gröbner基。

定义5.3 设C和C'是上述两个电路,在其变量上m个

的多项式序列称为切片多项式序列,如果

,

那么多项式

就称为

序列的切片关系。

定理5.4 设C和C'是上述两个电路,

是定义4.3中定义的切片多项式序列。那么根据引理5.1,C和C'是等价的(

)当且仅当

。

证明:

根据定义5.3,得

设边界

这确保了所有的

都在

中。

包含所有的域多项式F,因此将它们添加到

中。最后,计算是否

。下面给出算法:

根据定理5.4,我们能推导出增量等价性验证算法。先固定边界

,并通过计算切片Gröbner基的

模的余数递归地导出

,

。通过计算最后

的结果。如果

,则乘法器电路C和C'是等价的。

6. 实验

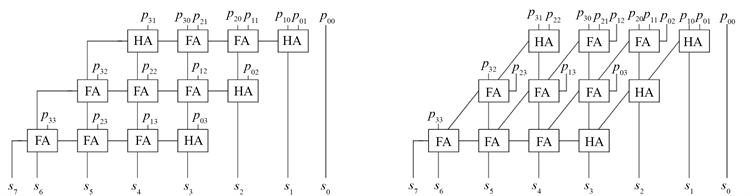

本文对两类整数乘法器进行等价性验证,分别是btor乘法器和sp-ar-rc乘法器。这两个乘法器都是根据推论3.2中的部分积作为两个输入位,然后由全加器和半加法器进行累加,如图2所示。

Figure 2. Structure of btor (left) and sp-ar-rc multipliers for

with

图2. 具有

的

的btor乘法器(左)和sp-ar-rc (右)乘法器的结构

图2是

的4位两输入的实验验证的两类乘法器的结构。在btor乘法器中,全加法器和半加法器以网格状结构累积(图2左侧);而在sp-ar-rc乘法器中,全加法器和半加法器是对角累积的(图2右侧)。我们使用工具aigmultopoloy [15],该工具以电路的AIG表示作为输入,并返回一个包含计算指令的文件。由于Mathematica输入语言更灵活,支持更多变量,被用作计算机代数系统,因而本文将这些指令传递给Mathematica。

实验使用了一台带有Ubuntu18.04虚拟机的笔记本电脑,配备Intel i5-8250 1.60 GHz CPU和4 GB主内存。运行时间限制设置为1200秒,主内存使用限制为4 GB。实验中的时间均以秒为单位列出。我们测量从aigmultopoloy开始到Mathematica 完成的时间,包括该aigmultopoloy工具生成Mathematica文件所需的时间和计算机代数系统的启动时间。在实验数据中用TO表示达到时间限制、MO表示达到内存限制、EE表示状态错误。

如表1所示,无论是Lingeling还是ABC在n大于8位时,都超出实验设定的运行时间,而增量方法能验证达32位的这两类乘法器的等价性 [16]。在此基础上添加加法器重写(第六列),不仅能计算高达128位的等价性,同时8~32位乘法器的等价性验证也有着明显的加快。表中最后一列,不仅采用增量验证方法,还利用第四节中提到的Gröbner基消去,实验数据显示,与第六列相比对各位数乘法器的验证时间均略具优势。

7. 结论

本文基于Gröbner基着眼于结构相似的乘法器,采用了增量式的等价性验证算法。在这个基础上,添加加法器重写和Gröbner基消去的算法相关实现,并已于Linux系统中成功编译。实验对比不同方法进行等价性验证的运行时间,由实验数据易见,增量等价性验证能提高验证效率,并在此基础上进一步进行优化,其验证时间略具优势。未来如何将这些技术扩展到浮点运算,甚至更具挑战性的乘法器结构和其他算术电路还有待进一步研究。

NOTES

*通讯作者。