1. 引言

视频产业近年发展愈发迅猛,传统的图像采集方式采用单片机作为核心处理单元,效率低下,对串行数据的处理速率较慢。对于传统的视频图像传输方式来说,随着科技的发展和应用的深入,其局限性也日益显现出来。对于一些需要长距离、高质量视频传输的应用场景,传统的视频传输方式往往难以满足需求,或者需要付出较高的成本。此外,对于一些移动设备或临时应用场景,传统的视频传输方式也可能因为布线困难、维护不易等问题而难以适用。FPGA中文名现场可编程门阵列,相比与单片机集成电路的传统结构,在视频图像信息处理方面集成度高,内部资源丰富,可塑性更强 [1] 。随着以太网技术的不断发展和FPGA的广泛应用,以太网和FPGA的结合为视频传输系统的设计提供了新的思路。以太网作为一种高速、稳定的网络传输技术,已经成为现代通信领域的主流技术之一。而FPGA有强大的并行计算能力和高度的灵活性,可用于实现各种数字信号处理算法。本文将以太网和FPGA相结合,设计了一种高效、稳定的视频传输系统,旨在满足日益增长的视频传输需求,为视频传输领域的发展注入新的活力。

2. 总体系统设计

图像传输系统总体设计如图1所示。

本次FPGA芯片选用Altera系列的EP4CE10F17C8板卡。系统开始工作时由时钟生成模块为整个系统提供工作时钟。上电后首先开始驱动摄像头工作,将传输协议写入摄像头寄存器进行初始化配置。配置完成后即开始采集图像,采集到的数据先缓存到FPGA的SDRAM当中并进行简单处理,由FIFO控制数据处理逻辑 [2] ,再通过图像格式配置将图像信息处理成相应的传输格式 [3] 。之后将图像信息打包成以太网数据包,经过以太网发送到上位机。在上位机端进行数据解包,还原出原始图像信息,观察并验证结果。

3. 系统模块设计

3.1. ov7725

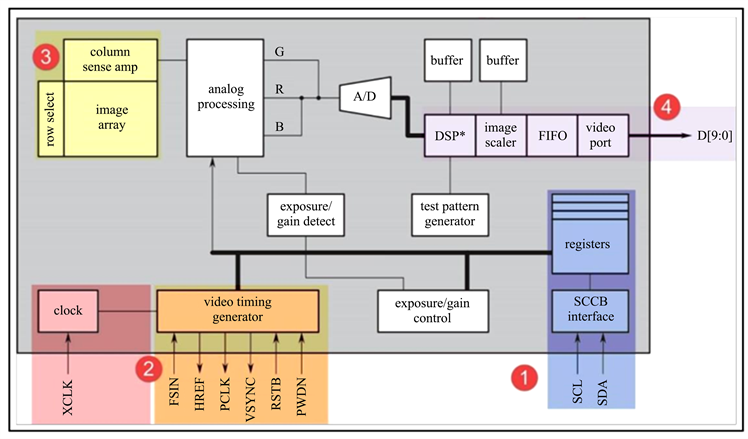

系统的图像信息采集主要由摄像头ov7725完成,光线通过镜头投射到ov7725的图像传感器表面上,图像传感器将接收到的光学图像转换为电信号,这些电信号随后被转换为数字图像信号,转换后的数字图像信号被送到数字信号处理芯片中进行加工处理,其内部功能框图如图2所示。

Figure 2. Internal function block diagram

图2. 内部功能框图

(1) 控制寄存器

图2中标号1的位置是ov7725的控制寄存器,它根据这些寄存器配置的参数来运行。配置的参数由外部控制器即FPGA通过SDA和SCL引脚来写入。

(2) 通信、控制信号及时钟

图2标号2处包含了ov7725的通信、控制信号及外部时钟,其中PCLK、HREF及VSYNC分别是像素同步时钟、行同步信号以及帧同步信号 [4] 。RSTB引脚为低电平时,用于复位整个传感器芯片,PWDN用于控制芯片进入低功耗模式。XCLK用于驱动整个传感器芯片的时钟信号,由外部输入;而PCLK是ov7725输出数据时的同步信号,由内部输出。

(3) 感光矩阵

图2标号3处的是感光矩阵,光信号在这里转化成电信号,经过各种处理,这些信号存储成由一个个像素点表示的数字图像。

(4) 数据输入信号

图2标号4处包含了DSP处理单元 [5] ,它会根据控制寄存器的配置做一些基本的图像处理运算。这部分还包含了图像格式转换单元及压缩单元,转换出的数据最终通过D0-D9引脚输出。

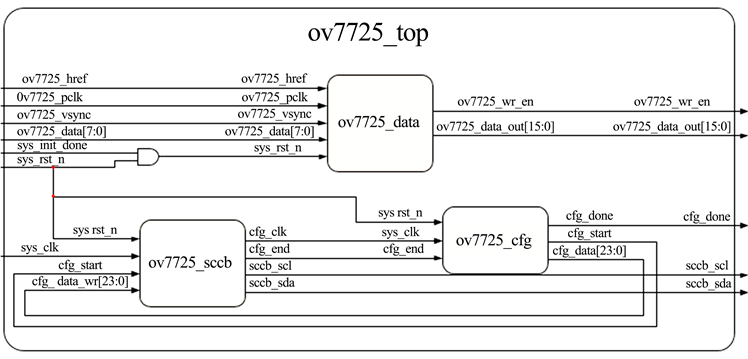

3.2. 图像采集模块

ov7725内部例化了SSCB协议(ov7725_sccb),寄存器配置(ov7725_cfg)以及图像采集(ov7725_data)等三个模块共同工作。配置好SCCB协议与寄存器过后,图像采集模块开始工作。时钟信号为ov7725_pclk,由ov7725摄像头自带晶振产生并传入,频率24MHz,作为模块工作时钟;复位信号sys_rst_n,低电平有效;ov7725_vsync为摄像头采集图像的场同步信号;ov7725_href为行有效图像使能信号,信号只有采集图像行有效显示区域为高电平,其他时刻为低电平,ov7725_data位宽为8bit,采集的图像数据分两次传入模块,先传入图像数据高字节,下个时钟周期传入低字节,所以显示图像就需要对传入图像数据进行拼接,拼接后的数据做一下缓存输出写入SDRAM [6] 。而且摄像头刚采集的前几帧图像数据不太稳定,先舍弃前10帧图像。图像采集功能模块如图3所示。

Figure 3. Image acquisition function module diagram

图3. 图像采集功能模块图

3.3. 以太网通信

3.3.1. 通信协议

本次以太网传输基于UDP协议,该协议的功能主要是将图像信息数据封装成特定格式,而UDP协议是一个基于IP协议,所以打包每个传输数据时需要在UDP数据基础上加上IP包头信息,就能得到IP层的数据内容 [7] 。IP层经MAC层发送,因此在其数据基础上再加上MAC帧头以及校验字段,即可得到MAC层数据内容,系统中的MAC层即FPGA板载,三者之间的关系如图4所示。

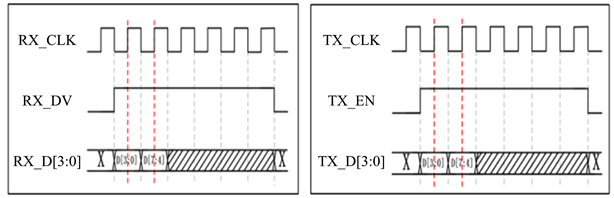

除了以上数据层之间的联系,在传输过程中还需要转换芯片PHY,MAC层与PHY之间的连接使用的是MII接口协议 [8] 。在MII接口协议中,每个时钟周期只传输4位数据,数据传输时先发送字节的低4位,再发送字节的高4位,数据和使能信号在时钟的下降沿变化,时钟上升沿可以采集到数据稳定状态。MII接口数据接收、发送时序图如图5所示。

Figure 5. The MII protocol timing diagram

图5. MII协议时序图

在数据传输过程中,MAC层将数据发送到TXD信号线上,并通过TX_EN信号线指示PHY层进行数据的发送。PHY层在接收到TX_EN信号后,将数据从TXD信号线上读取,并通过物理层进行发送。同时,PHY层还会通过RX_DV信号线指示MAC层有数据接收。

3.3.2. 图像数据打包

数据打包是读取SDRAM中待发送的图像数据按照上位机格式进行数据打包并发送,并且在上位机能接收到完整的图像数据,获取图像信息。一个完整的图像数据协议包括:4字节包头数据、1字节设备地址、包长度、指令、图像数据、CRC校验位。图像数据包协议见表1。其中,包头和设备地址字段主要添加以太网帧的头部信息,包括源MAC地址、目标MAC地址等 [9] 。指令和包长度字段用于标识数据包中携带的长度信息和数据类型。

Table 1. Image data package protocol

表1. 图像数据包协议

本次传输的图像格式为RGB565,分辨率为640 * 480。一帧完整的图像分为75个数据包传输,一个包包含有效像素8192字节。每传输一个数据包图像信息,每帧的第一个数据包对应添加包头,校验地址,包长度及指令等信息,相应的校验信息也会添加在末尾。数据包抓取如图6所示。

3.3.3. 图像数据接收

接收端接收到的数据是一个个完整的以太网数据包,此时进行地址校验与数据提取,在模块内定义7个状态,状态跳转图如图7所示。

数据包以字节为单位,以太网数据包中的各类型数据的字节宽度包含在数据中的,利用字节宽度信息作为状态机跳转的约束条件 [10] 。

(1) 初始状态:

系统上电后,模块内状态机一直处于初始状态,在系统时钟上升沿,当检测到数据使能信号为高电平、拼接数据为8'h55时,使能信号拉高一个时钟周期,状态机跳转到数据包头接收状态。

(2) 数据包头接收状态:

在数据包头接收状态内,完成前导码+帧起始界定符的接收与检验。声明字节计数器,初值为0,状态机处于数据包头接收状态时,数据使能信号拉高一次,计数器自加1。计数值为6,拼接数据为8'hd5,帧起始界定符通过检验,计数器归零,使能信号拉高一个时钟周期,状态机跳转到以太网帧头接收状态。

(3) 以太网帧头接收状态:

此状态内会接收14字节数据,包括6字节的目的MAC地址、6字节源MAC地址、2字节长度/类型字节。其中0-5字节就是要校验的目的MAC地址。当MAC地址寄存器寄存的MAC地址与板卡MAC地址相同时,标志信号保持高电平。14个字节接收完毕,标志信号mac-flag信号为高电平,表示目的MAC地址正确,状态机跳转到IP首部接收状态。

(4) IP首部接收状态:

校验IP地址,地址校验通过状态跳转到UDP首部接收状态,校验不通过就跳转到初始状态。

(5) UDP首部接收状态:

UDP首部包含8字节数据,分别是源端口、目的端口、数据长度(UDP首部 + 数据长度)、checksum校验字节,其中第5、6字节包含数据长度信息,在此状态只提取数据长度信息,为后面数据接收做准备。

(6) 有效数据接收状态:

有效数据的字节长度是要在数据字节长度基础上减去UDP首部的字节长度。利用寄存器寄存有效数据字节长度信息。同时,字节计数器对传入的有效字节数据进行计数,有效数据接收完毕,计数器归0,使能信号拉高一个时钟周期,状态机跳转到结束状态。

(7) 结束状态:

在结束状态中,当数据使能信号为低电平时,以太网数据接收完毕,状态机跳回到初始状态,等待下一个以太网数据包的传入。

4. 仿真与验证

系统验证

本次在日常生活环境中进行了模拟测试,验证系统的正确性。在上位机端使用了wireshark和网络调试助手进行验证,验证以太网传输的图像数据的准确性,如图8所示。

Figure 8. The upper position machine displays figure

图8. 上位机显示图

系统整体如图9所示,各项参数见表2。

5. 结论

基于FPGA的以太网视频图像传输系统在设计上充分发挥了FPGA的并行处理和灵活配置的优势,结合以太网的高速传输特性,实现了高效、稳定的视频传输。该系统在实际应用中,不仅提高了视频传输的质量和实时性,还为各种视频传输应用场景提供了更大的灵活性和可扩展性 [11] 。随着技术的不断进步,我们相信基于FPGA的以太网视频传输系统将会在未来发挥更大的作用,满足更为复杂和多样化的需求。

NOTES

*通讯作者。