1. 引言

空间飞行器数字系统主要由FPGA、CPU、DSP等数字器件构成。由于其工作在含有大量辐射粒子的宇宙环境下,单粒子翻转等软错误对飞行器的安全性、可靠性造成了很大的威胁 [1]。为了保证飞行器的长寿命和高可靠性,开展FPGA、CPU等器件的软错误检测技术研究,以便评估出这些器件的单粒子翻转敏感特性 [2],为空间飞行器数字系统的设计选型和防护设计评价提供依据和支撑,对寻找预防和减缓空间效应措施具有极大的意义和价值 [3]。

论文以TI公司的TMS570LS3137型号CPU和Xilinx公司的Virtex5 XC5VFX130T器件等两类新型COTS器件为电离辐射摸底试验的试验对象,针对器件的不同资源,分别构建两类器件单粒子翻转测试系统,以评估不同测试状态下器件本身的单粒子翻转敏感程度,为后续的抗辐射加固设计提供依据,达到指导其未来宇航应用的目的。

2. 测试系统的总体结构设计

2.1. 系统功能需求分析

为了验证在实际辐照环境下软错误检测方法的有效性,需要搭建一个可以用于辐照试验的软错误测试系统。一般来说,测试系统可以控制试验过程,并且能够采集、传输、处理、保存试验数据 [4] [5] [6]。为此,该测试系统包含以下的功能:

1) 对辐照试验过程进行控制。因为需要对FPGA和CPU两种器件进行辐照试验且这两种器件必须分开独立进行。因此,要求测试系统能够在FPGA测试和CPU测试之间自由切换,并可以选择具体的针对器件某一主要资源的测试模式。此外,测试系统应该可以控制一次试验的开始、暂停或者结束。

2) 回读被测FPGA。这是评估配置存储器软错误敏感性的关键步骤。为此,要求测试系统通过一个读写速度很快的接口来对被测FPGA进行回读,并能够快速且可靠地将回读数据上传。该测试系统选用SelectMAP接口回读FPGA并使用网口上传数据。

3) 实时上传FPGA动态测试及CPU测试的软错误数量。在实际辐照试验中,需要确定刚出现软错误的LET值及软错误数量的饱和值。因此,测试系统应该能够实时观测测试数据。

4) 保存上传的测试结果。测试系统不仅可以实时采集辐照试验数据,而且能可靠地将其保存,以供进一步的处理。

2.2. 系统总体架构设计

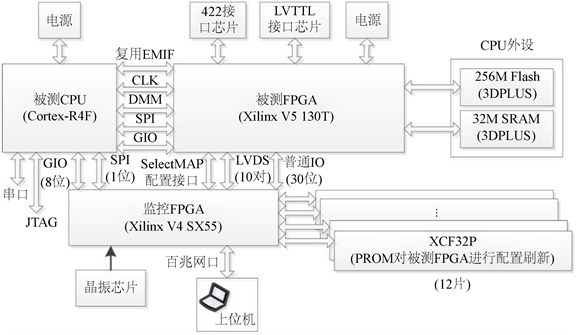

一般将被测器件放在真空中,以避免加速器中射出的高能粒子到达芯片表面过程中能量衰减过多,这也导致了对外界环境和被测芯片之间的连线类型和数量的要求很苛刻。此外,为防止加速器对试验人员产生辐射伤害,实际操作中试验人员一般通过计算机对测试系统进行远程操作。为此,将软错误测试系统分为监控FPGA、被测FPGA、CPU、上位机等主要部分。测试系统的总体结构如图1所示。

Figure 1. Overall structure of single particle soft error test system

图1. 单粒子软错误测试系统总体结构

图1中,

1) 上位机

试验时上位机一般处于真空室外,在辐照过程中由控制室的计算机远程控制,监控FPGA通过用户数据报协议(UDP)与PC进行数据传输,以达到测试环境要求的高速可靠的数据交互和板间最少连线的双重目的。

上位机作为测试系统控制中心与数据存储与分析平台,设置测试条件与参数;向下位机发送测试模式切换、测试过程控制等指令;静态测试模式下,回读被测FPGA的配置数据并与参照文件比较;实时统计FPGA动态测试以及CPU测试的翻转数量;保存每一次测试的数据和结果,用于后续数据分析。

2) 监控FPGA

监控FPGA通过网口与上位机直接相连,其主要功能有接收上位机下发的测试控制指令并执行相应操作;CPU测试模式下给被测FPGA提供时钟;将测试结果通过网口上传给上位机。

监控FPGA主要由以下模块组成:

a) 网口驱动模块,上位计算机与测试板的通讯接口。上位计算机通过网口向测试板发送各种控制命令;测试板通过网口向上位计算机传回测试状态与测试数据。采用UDP通讯协议实现。

b) 静态测试模块,采用“一次回读”的方式,即辐照一段时间后再对被测FPGA通过SelectMAP口回读,并区分出配置存储器和BRAM的配置信息。

c) 动态测试模块,为BRAM和触发器动态测试提供输入时钟,并接收测试输出。与静态测试“先辐照后统计”不同的是,在被测FPGA被辐照的同时,该模块统计翻转位数,即“边辐照边统计”。

3) 被测FPGA和CPU

FPGA软错误检测方法以测试电路的形式在被测FPGA中实现。FPGA测试模式下,被测FPGA的功能主要有静态测试模式下,通过SelectMAP口将配置数据发给监控FPGA;动态测试模式下,通过信号线将测试电路的输出结果上传给监控FPGA。而在CPU测试模式下,被测FPGA的功能是接收来自CPU的测试数据并将其转发给监控FPGA。

CPU软错误检测方法以测试程序的形式在被测CPU中实现。CPU的功能主要有实现寄存器、SRAM、Flash等资源的测试程序;通过串口与上位机直接相连,在CPU测试过程中向上位机打印测试相关的信息。

2.3. 系统硬件连接设计

测试系统的硬件平台主要由被测器件(FPGA和CPU)、监控FPGA、上位机以及一些外设构成。如图2所示,被测FPGA与监控FPGA之间有配置接口、普通I/O和LVDS I/O;被测FPGA外接了Flash、SRAM和SDRAM,这三类存储器件用于CPU器件使用;晶振、电源、422接口芯片、LVDS接口芯片等外设也与被测FPGA相连;与监控FPGA相连的存储器件为12片PROM (XCF32PV048C),每一片存储空间为32 Mb,而一片XC5VFX130T需要2片PROM存储设计文件;另外,监控FPGA通过百兆网口与上位机进行连接。

Figure 2. Hardware connection diagram of test system

图2. 测试系统硬件连接图

由图2可以看出,测试系统接口众多且复杂。被测FPGA与监控FPGA之间的接口,如表1所示。

Table 1. Interface table of tested FPGA and monitoring FPGA

表1. 被测FPGA与监控FPGA接口表

3. 系统逻辑设计与实现

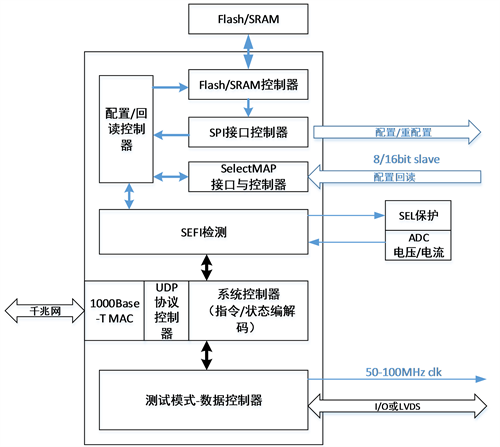

3.1. 监控FPGA设计

监控FPGA接收上位机测试指令、测试参数、测试芯片配置数据;按上位机测试参数设置被测FPGA芯片的工作时钟、测试模式;测试SEFI接口;配置和刷新测试芯片的配置存储器;回读测试芯片的配置信息;接收测试芯片的测试数据;采用UDP协议上传测试结果。监控FPGA的逻辑设计如图3所示。

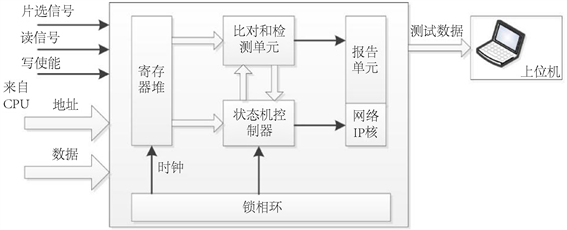

3.2. 被测FPGA设计

FPGA和CPU两种器件的软错误测试都将用到了被测FPGA,然而不同测试模式下,被测FPGA的逻辑设计是不同的。首先对于FPGA测试模式,考虑到对被测芯片进行多项目测试的需求,被测芯片需根据测试需要加载不同配置,并根据需要测试SEFI和回读配置存储器数据,且监控芯片有充足的设计资源可用,方案拟采用基于被测FPGA芯片的被动模式SelectMAP端口,由监控芯片作主控器件对被测FPGA芯片进行SEFI测试、器件配置和配置数据回读,同时使用LVDS与被测FPGA动态测试电路接口,控制被测FPGA的动态测试模式并接收其测试结果数据。FPGA测试模式下被测FPGA的逻辑设计如图4所示。

Figure 3. Logic design of monitoring FPGA

图3. 监控FPGA逻辑设计

Figure 4. Logic design of tested FPGA in FPGA test mode

图4. FPGA测试模式下被测FPGA逻辑设计

对于CPU测试模式,不同的测试程序,需要通过Xilinx软件设计不同的被测FPGA内部结构,该结构与CPU一侧是EMIF接口,与上位机一侧是网口通信。CPU测试模式下被测FPGA的逻辑设计如图5所示。

Figure 5. Logic design of FPGA under test mode of CPU

图5. CPU测试模式下被测FPGA逻辑设计

图5中REGs Unit单元锁通过DMA推送来自CPU的数据流。Sate Machine控制当前的数据流检测和逻辑判断,并根据结构决定是否需要将当前的结果上报给上位机。网络接口协议自定义,核心是将当前发生SEU的SRAM/Flash地址、寄存器编号、中断索引和数据内容上传给上位机,上位机进行实时/离线分析处理,完成测试。

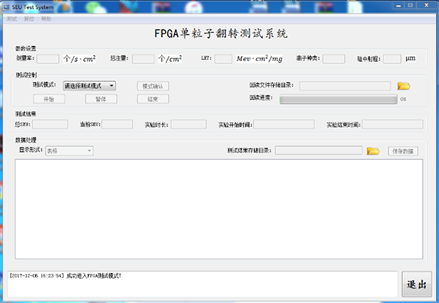

4. 系统应用验证

选取FPGA测试模式下的“静态测试”和CPU测试模式下的“寄存器测试(全0)”对设计实现的测试系统进行了应用验证。

1) FPGA测试模式下的“静态测试”

上位机软件启动后,点击主界面左上角的“测试”菜单,选择“FPGA测试”,进入FPGA测试模式,如图6所示。

Figure 6. Main interface of FPGA test

图6. FPGA测试主界面

参数设置完毕后,点击“开始”按钮,上位机记录实验开始时间并计时。辐照一段时间后,点击“暂停”按钮,上位机停止计时并记录下实验结束时间后,立即开始回读。回读结束后,统计软错误数量。“当前SEU”由两部分组成,分别是CLB和BRAM互联资源的翻转数和BRAM的翻转数。点击“结束”按钮,上位机提示试验人员存储测试结果。在当前路径下选择“静态测试”文件夹作为数据保存的目录,最后一步是点击“保存数据”,实验数据即存到了上一步指定的文件夹中,如图7所示。

Figure 7. FPGA static test result storage

图7. FPGA“静态测试”结果存储

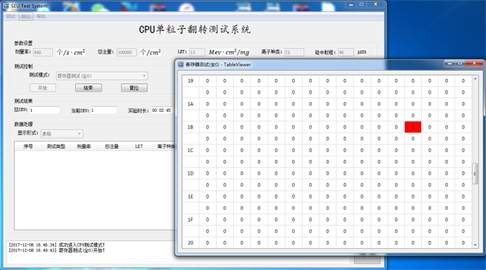

2) CPU测试模式下的“寄存器测试(全0)”

如图8所示,进入CPU测试模式。设置好剂量率等参数后,先选择并打开正确的串口以连接CPU,并选择一个文件夹作为测试结果的存储目录。点击“开始”按钮,上位机记录下实验开始时间并计时,并弹窗显示当前寄存器的各地址及其对应的初始值(都为0)。在测试过程中,CPU扫描到一个软错误,即地址为1B,第4位发生了“0跳变为1”的SEU。上位机在后台自动保存了该数据,在主界面上更新了“总SEU”和“当前SEU”的同时,在弹窗中标注了软错误发生的位置,如图9所示。

Figure 9. Upper computer processing test data

图9. 上位机处理测试数据

点击“结束”按钮后,上位机将当前系统时间作为测试完成的时间,此时试验人员可以选择变更辐照参数,继续开始下一次测试,或者点击“保存数据”按钮后,切换测试模式,如图10所示。

5. 小结

论文以TI公司的TMS570LS3137型号CPU和Xilinx公司的Virtex5 XC5VFX130T器件等两类新型COTS器件为电离辐射摸底试验的试验对象,从测试系统的功能需求出发,对系统进行功能定义以及模块划分,并提出系统的总体结构设计,完成了测试系统的硬件平台、以及包括监控FPGA和被测器件在内的软件逻辑设计和实现。应用表明,该测试系统可以很好地满足实际测试需求。

基金项目

国家某重点科研项目(MJ-2016-S-42, MJ-2018-S-34),国防基础科研计划项目,国网浙江省电力有限公司科技项目(2020年),陕西省创新能力支撑计划项目(2019PT-03),电子元器件可靠性物理及其应用技术重点实验室开放基金(ZHD201603)。