1. 引言

碳化硅(SiC)材料是目前世界上公认的绿色高效的新型半导体材料,具有宽禁带宽度、高击穿电场、高热导率、高饱和电子漂移速度、抗辐射能力强以及化学性质稳定等优势(材料性能对比见表1),使得SiC成为制备新型电力电子器件的立项材料,尤其适用于高压、高频、大功率、高辐照以及某些波长的光电探测技术领域 [1]。因此,SiC器件是下一代大功率电力电子器件的最优秀代表,具有推动电网装备革命性变革的潜力,是未来电力电子装备竞争的核心。自上世纪90年代开始,电力电子器件的研究人员就将目光转移到SiC等具有更优电气性能的宽禁带半导体材料上。SiC是目前发展最成熟的第三代宽禁带半导体材料,击穿电场强度比硅材料高一个数量级,从而在相同的外延厚度和掺杂浓度下,可以实现更高的击穿电压;载流子的饱和迁移率更高,从而可以在更高的频率下工作;导热性能良好,可以得到更大的功率密度,因而非常适合制作高温、高频、大功率电子器件,并将在电力电子领域得到广泛应用。

Table 1. Comparison table of material parameters of silicon carbide and silicon

表1. SiC和Si的材料参数对比表 [2] [3] [4] [5] [6]

各种功率器件中,SiC MOSFET是一种理想的开关器件和线性放大器件。它具有开关速度快,开关损耗小;保真度高,非线性失真小;工作频率高,频率响应好;热稳定性高,安全工作区宽;输入阻抗高,增益大,驱动功率小,驱动电路简单等优点,在功率器件中占有极为重要的地位。在传统的Si功率MOSFET中,其电流输出能力受限于同时兼顾降低导通电阻和提高击穿电压这一矛盾关系上,为了获得高的击穿电压,必须采用高电阻率的漂移区,这对MOSFET而言是很多的弊端。由于SiC材料有高于Si材料的临界击穿电场,对于给定的击穿电压,选取薄的轻掺杂漂移区,SiC MOSFET的导通电阻至少要比Si MOSFET小两个数量级,特别是高击穿电压,SiC MOSFET更具有优势。因此,SiC MOSFET在低功耗、高频开关领域得到了广泛应用。可以说,SiC器件将是带动未来新能源技术革命的“绿色能源”器件。

在SiC MOSFET器件制备工艺中,多晶硅(Polysilicon)被广泛用于栅电极,多晶电极对关键线宽(CD)要求极高,业界趋向于采用较低的射频能量并能产生低压和高密度的等离子体来实现多晶硅的干法刻蚀。其中感应耦合等离子刻蚀技术(ICP)得到大力应用 [7] [8]。随着功率器件尺寸的不断缩小,多晶硅栅的刻蚀越来越具有难度和挑战性。此外,作为栅电极的多晶硅需要通过掺杂磷元素的手段来实现更好的电导通特性,多晶原位掺杂对设备能力要求较高,当前业界仍多采用离子注入和退火推结的方式对多晶硅进行掺杂磷处理。与本研究相关的多组实验证明,掺磷扩散后的多晶硅表面完全不同于未掺杂多晶硅,这对干法刻蚀形貌提出了更高的要求,本文详细讲述了如何优化掺磷后多晶硅的干法刻蚀,最终成功应用于6500 V/20 A SiC MOSFET产品,电学性能表现优异。

2. 多晶硅的刻蚀机理

为了保护MOSFET的栅极氧化层不被损伤,通常要把多晶硅刻蚀分成几个步骤:主刻蚀、着陆刻蚀和过刻蚀 [9] [10]。主刻蚀通常有比较高的刻蚀速率,但是对氧化硅的选择比较小。通过主刻蚀可基本决定多晶硅的剖面轮廓和关键尺寸。着陆刻蚀通常对栅极氧化层有比较高的选择比以确保栅极氧化层不被损伤。一旦触及到栅极氧化层后就必须转成对氧化硅选择比更高的过刻蚀步骤以确保把残余的硅清除干净而不损伤到栅极氧化层。

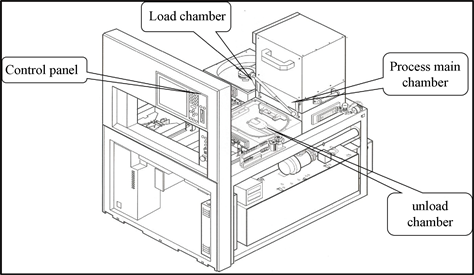

本文涉及的干法刻蚀工艺采用的是反应离子刻蚀(RIE)刻蚀方式,设备包括传送系统、工艺主腔、RF射频电源、真空系统、特气系统及终点检测系统,如图1所示。

Figure 1. Schematic diagram of reactive ion etching equipment

图1. 反应离子刻蚀设备的示意图

刻蚀终点检测系统的原理如下,当发生侧面刻蚀时,可以借助于使刻蚀减少到最低量从而能控制线宽和边缘剖面到一定的成都。具体方法包括:

1) 刻蚀层的直接宏观检测;

2) 监测从刻蚀层的发射出的光波;

3) 用发射光谱法对等离子体刻蚀剂粒子的浓度检测;

4) 用发射光谱法或质谱法对刻蚀产物的检测;

5) 等离子体阻抗变化的检测。

终点检测对于刻蚀中工艺控制和工艺判断,都是一个有用的辅助手段,可以使材料组份和厚度的波动或工作参数的改变而引起的刻蚀速率的变化得到补偿。

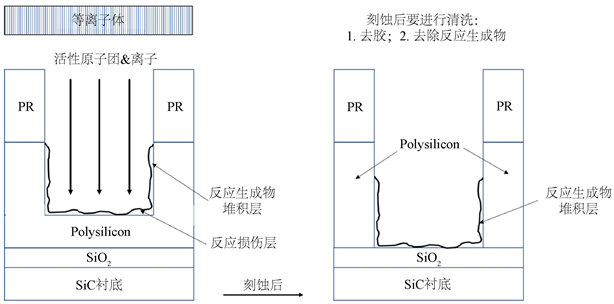

多晶硅刻蚀原理(如图2所示),F原子对Si的刻蚀是各向同性的,所以以F原子为基础的化合物气体如CF4、SF6等都不适宜用作多晶硅的刻蚀气体;而Cl原子对硅具有的各向异性刻蚀作用,所以Cl2、HCl、SiCl4等气体都可以被采用。使用这些气体还有一个好处是,以Cl所形成的等离子体对Si及SiO2刻蚀的选择比较好,因此在多晶硅刻蚀结束后,可以使用同样性质的等离子体对聚酰亚胺(Polycide)进行过刻蚀,以确保多晶硅被刻净,而又不会刻蚀太多的SiO2层 [11] [12] [13]。

Figure 2. Schematic diagram of polysilicon etching mechanism

图2. 多晶硅刻蚀机理示意图

平面型SiCMOSFET栅结构 [14] [15] 采用的多晶硅沟槽深度为5000 A,属于浅沟槽刻蚀,其难点在于沟槽深度的均匀性控制,此外,为了满足沟槽隔离氧化物的填充要求,沟槽剖面轮廓的控制也非常重要,因为太垂直的轮廓不利于化学气相沉积(CVD)的沉积,通常会要求有适当的倾斜度。随着工艺尺寸的缩小,要求达到更高的深宽比使得剖面轮廓控制和深度均匀性控制受到更大的挑战。当然CD的均匀性和剩余栅氧化层的均匀性也是重要的技术指标。对于浅沟槽的刻蚀,Cl2和HBr依然是主刻蚀气体,再配合小流量的氧气和氮气来产生氮氧化硅形成侧壁钝化层从而达到理想的刻蚀剖面轮廓,Ar和He通常用作辅助稀释的作用。由于沟槽底部轮廓同样影响到氧化物的填充,采用Cl2作为主刻蚀的气体容易形成比较直的剖面轮廓和凸型的底部轮廓,采用HBr作为主刻蚀气体能得到比较斜的剖面轮廓和凹形的底部轮廓 [16] [17]。

3. 掺杂对多晶硅刻蚀效果的影响

3.1. 多晶硅刻蚀基础参数

本文采用的主刻蚀气体为Cl2,工艺菜单(Recipe)关键参数如表2所示。实测刻蚀速率为2892.0 A/min,片内均匀性3.8%。该工艺参数下,氧化硅(oxide)的刻蚀速率为27 A/min。计算其选择比(oxide: Poly-Si)为1:107。

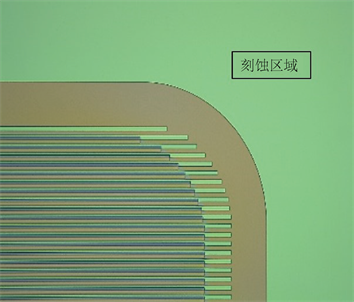

采用当前的Recipe刻蚀未经磷掺杂的多晶硅后,可以得到理想表面形貌(见图3所示),刻蚀区域无异常颗粒,且对多晶下的氧化层损失很小,显微镜观测为颜色均匀一致的介质层。

Table 2. Main etching menu of Polysilicon

表2. 多晶硅主刻蚀菜单

Figure 3. The appearance of undoped polysilicon etching

图3. 无掺杂的多晶硅刻蚀后,外观无残留颗粒

3.2. 多晶硅掺杂磷工艺

多晶硅在MOSFET器件上的应用之一为栅电极 [18],为形成低电阻率的多晶硅,通常需对多晶硅栅电极进行掺杂,在该掺杂过程中,由于离子注入相对具有可控性好等优点,被广泛用来掺杂形成多晶硅栅电极。本文涉及的工艺路线采用离子注入方式进行掺杂,具体流程如表3所示:

Table 3. Etching process flow after polysilicon doping

表3. 多晶硅掺杂后的刻蚀工艺流程

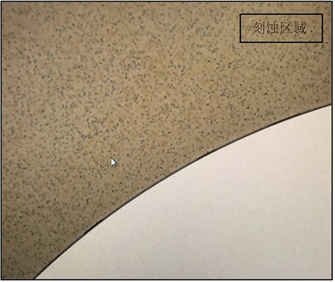

注入掺杂时会产生晶格损伤,为恢复晶格、激活杂质,电性能还原会进行损伤退火,损伤退火的方式为常压炉管900℃高温处理30到60分钟,通过退火处理后多晶膜质会发生变化。经过光刻与刻蚀后镜检表面显示刻蚀区域均布颗粒,局部放大为100倍后如下图4所示,介质层上黑色颗粒分布明显。

Figure 4. The appearance of doped polysilicon etching

图4. 掺杂的多晶硅刻蚀后,表面残留颗粒

4. 多晶硅刻蚀工艺优化

4.1. 异常颗粒的表征与分析

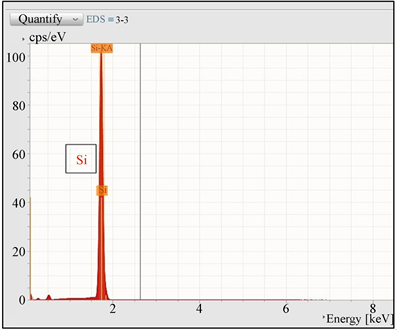

针对掺杂多晶硅刻蚀后的表面异常颗粒进行能谱分析(EDS),如下图5所示,成分扫描结果显示异常颗粒元素为Si。

Figure 5. EDS composition analysis results of abnormal etching particles

图5. 刻蚀异常颗粒EDS成分分析结果

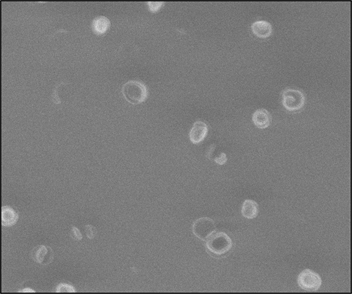

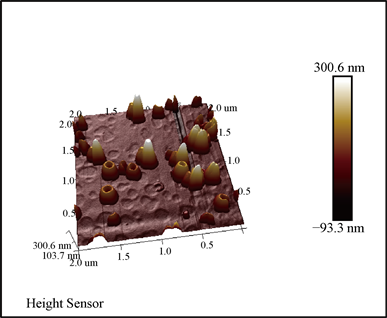

使用扫描电子显微镜(SEM)对表面颗粒进行微观辨识,如图6所示,颗粒直径约200 nm。采用原子粒显微镜(AFM)对异常颗粒进行扫描分析,如图7所示,残留颗粒为高度100~300 nm的凸起。

Figure 6. SEM composition analysis results of abnormal etching particles

图6. 刻蚀异常颗粒SEM表面扫描结果

Figure 7. Protruding 3D morphology of abnormal particles

图7. 异常颗粒凸起3D形貌

结合以上现象及解析结果分析,确认刻蚀后颗粒物为多晶残留。从以上实验得出结论,经过离子注入掺磷及高温退火炉处理后的多晶硅,直接光刻、刻蚀后,表面会出现较严重残留。

4.2. 残留颗粒的引入分析及工艺优化

掺杂后高温推结所采用的的高温退火炉为常压炉管,退火条件为900℃,工艺时非真空状态,惰性气氛为N2环境,在高温处理阶段炉内会残余少量的O2,致使多晶硅发生氧化。从基础参数里已知,氧化硅和多晶硅的刻蚀选择比达到1:107,多晶硅上即使有几百A的氧化层,刻蚀后也会造成残留。

为证实是由于高温推结处理使多晶硅表面形成氧化层,从而造成刻蚀残留的现象,对掺杂推结后的多晶硅表面进行湿法预处理后再观察。

4.2.1. 采用DHF表面处理

硅片生长100 nm SiO2,常规工艺生长500 nm Poly-Si,掺杂P后进入高温退火炉进行推结,采用湿法的DHF (HF:H2O = 1:50)对表面进行预处理2分钟。整面刻蚀后确认外观有少量残留,如图8的暗场镜检结果所示,残留现象有改善,但是表面仍有少量颗粒残留(暗场下的亮点为异常位置)。

Figure 8. Etched surface morphology after DHF rinse for 2 mins (Microscope dark field)

图8. DHF漂洗2 mins后刻蚀表面形貌(显微镜暗场)

增加DHF湿法处理时间为10 mins,腐蚀速率为50 A/Min,整面刻蚀,检查外观,图8所示的亮点位置全部消除,表面已无颗粒残留。

4.2.2. 工艺优化及实际应用

从上述实验可知,增加表面DHF预处理后,刻蚀无残留,因此将此工步增加在完整的工艺流程中。如表4所示:

Table 4. Polycrystalline phosphor expanded etching process (optimized)

表4. 多晶磷扩后刻蚀工艺流程(增加DHF漂洗步骤)

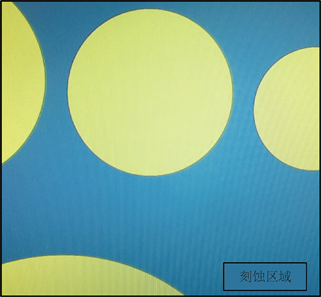

刻蚀后镜检结果见图9,刻蚀区域多晶已完全去除,且无任何颗粒残留物。(注释:图9的圆形区域为被光刻胶保护的多晶硅电极区,非圆形区域为刻蚀区域,多晶硅被刻蚀干净后可见颜色一致的氧化层介质)。

Figure 9. Polysilicon etching result after optimized process

图9. 优化工艺后的多晶硅刻蚀结果

将以上经优化后的多晶硅栅刻蚀工艺流程应用于一款6500 V/20 A SiC MOSFET芯片制备,实测其输出特性如下图10所示。VGS ≤ 8 V时,器件可稳定工作在饱和区域;VGS > 8 V时,表现出良好的压控特性,Id < 20 A的工作电流下,Vds < 5 V,该器件可持续工作在可变电阻区。

Figure 10. Output characteristic curve of a 6500 V/20 A SiC MOSFET

图10. 6500 V/20 A SiC MOSFET的输出特性曲线

5. 结论

本文通过工艺实验及理论分析,优化了掺杂多晶硅的刻蚀工艺步骤,采取DHF对多晶硅表面预处理的方式,有效去除了刻蚀后的表面颗粒残留。将优化工艺应用于一款6500 V/20 ASiC MOSFET中,器件表现出良好的输出特性。最后,作者将本研究工作中所提出的工艺要点总结如下:

1) 在光刻前增加表面的DHF预处理,可以有效去除掺杂多晶刻蚀可能出现的颗粒残留,通过此方法适用于由于多晶掺杂工艺的变化进行的多晶刻蚀工艺。

2) 光刻前对多晶的表面处置只限定适用DHF,如使用BOE去除表面氧化物,有可能对多晶表面态有影响,造成外观异常,外观现象会造成光刻机无法识别。

3) 预处理后到刻蚀前的放置时间不同有可能影响刻蚀效果,DHF前处理时间10 mins只针对从预处理到刻蚀前放置时间不超于48小时,如放置时间较长,预处理时间要依据实际情况而定。

基金项目

国家电网公司科技项目《碳化硅MOSFET沟道自对准工艺研究》 (项目编号:5500-201958481A-0-0-00)。