1. 引言

第五代移动通信技术(5G)作为面向2020年之后的新一代移动通信技术,其通信网络已在全球范围内大规模部署 [1],但是在信息交互的深度和广度上还不足以满足未来社会的需求。当前移动通信技术已开始向6G逐步演进,6G无线通信网络将由陆地无线通信网络为主体,卫星、无人机(UAV)等非陆地网络为补充共同组成,可以满足天基、空基、陆基、海基多种场景用户需求,推动全球互联向立体化、深度化发展,实现多场景的智慧、深度、全息、泛在连接 [2] [3] [4]。

在移动通信技术向6G演进的过程中,移动数据流量呈爆炸式增长,频谱资源与功率资源日益紧缺,成为制约通信系统发展的瓶颈问题。多波束技术利用大规模天线阵列产生不同指向的多波束,有效挖掘空间维度资源,提升频谱效率和功率效率,已在地面和卫星通信系统中广泛使用。现有多波束技术以固定多波束技术为主,其波束形状、方向固定,不能充分挖掘空间维度潜力 [5]。动态多波束技术可以动态调整波束方向、波束宽度及波束能量,实时跟踪用户,准确指向服务用户,相比于固定多波束技术,可进一步降低用户间干扰,抑制波束间重叠,可以深度挖掘空间维度潜力。同时,动态多波束技术与宽带通信技术结合,能够进一步提高系统吞吐能力与频谱效率。

动态多波束通信系统涉及信道信息获取、波束权值计算、以及编码调制、多载波调制解调等基带信号处理 [6] [7] [8]。为了研究上述关键技术在实际系统中的有效性,原型通信系统的设计尤为重要,应具备以下特征:

· 基带算法的快速部署

· 支持大带宽和高吞吐能力

· 支持实时可配置波束成形的天线阵列

基于上述需求,本文设计了宽带动态多波束无线通信原型系统,如图1所示构建了X86通用服务器与FPGA融合的计算架构,结合X86服务器计算能力强、开发效率高的优点与FPGA高速并行数据处理能力,满足动态多波束技术中相关算法海量计算需求,并实现快速部署、验证先进无线基带算法;利用RFSoC芯片完成系统数字中频功能,实现宽带模拟数字信号转换;同时,本系统通过配置可编程射频相控阵天线,实现动态波束成形;最后,利用高速接口连接上述部分,保证海量数据传输的可靠性。

本文后续章节安排如下:章节2介绍本原型系统的硬件架构;章节3介绍算法软件实现部分,章节4介绍本原型的实验验证结果,章节5总结全文的主要成果。

Figure 1. Overall structure of prototype system

图1. 原型系统整体结构

2. 原型系统硬件架构

本文提出的原型系统,硬件架构由射频单元、宽带数字模拟转换与数字中频单元、X86 + FPGA融合计算单元和高速接口单元构成,可实现上、下行链路中海量基带信号处理、宽带模数/数模转换(RF-ADC/RF-DAC)、数字上变频(DUC)与数字下变频(DDC)、高速数据传输、多通道射频收发以及动态多波束成形等功能,可以解决制约宽带毫米波多波束通信系统发展的硬件瓶颈问题 [9]。

2.1. 射频单元

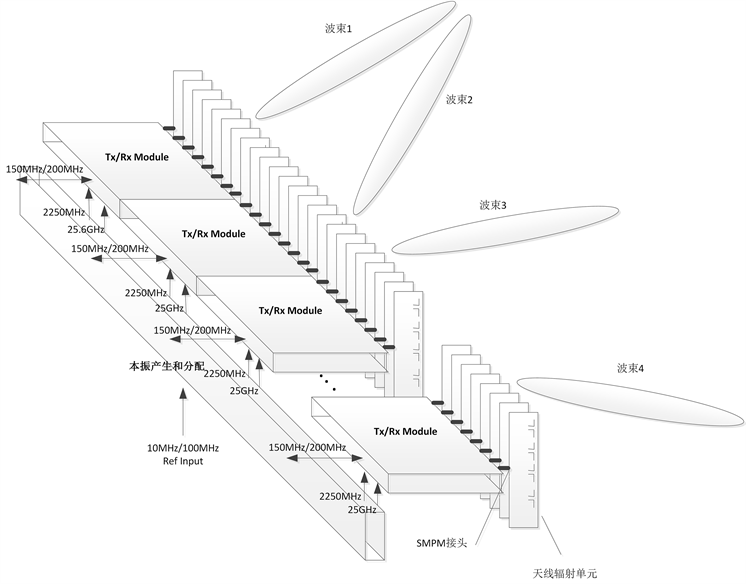

射频单元完成射频信号收发、波束成形、射频信号与模拟中频信号转换功能。如图2所示,射频相控阵天线包括TR组件、天线子单元以及本振子单元。其中,每个TR组件由一个1分8变频功分模块、数控接口板和8路TDD结构移相放大模块组成,8个移相放大模块通过行架连接成整体,功分变频板通过SMPM板–板射频连接器与8个TDD结构移相放大器模块相连,数控接口板负责根据基带侧发来的控制信号及时配置TR组件。天线子单元中,竖状排列的PCB板上印制偶极子天线,均采用垂直极化方式,4个偶极子天线合路为一个天线阵列,可实现垂直面40度波束宽度与水平面120度扫描角度。本振子单元中采用两次变频方案,分别变频至2800 MHz和28 GHz,本振信号分别为2650 MHz和25.2 GHz,其中2650 MHz本振采用100 MHz或10 MHz基准参考信号通过锁相环直接得到,25.2 GHz本振采用100 MHz或10 MHz基准信号直接锁定12.6 GHz DRO产生12.6 GHz信号后,再经过2倍频、滤波之后得到,两类本振信号分别通过1分8功分器即可得到8路对应的本振信号。整体结构为8个TR组件水平排列,每个TR组件的8个移相子通道对应8个天线阵列,可形成独立相扫波束,实现基带和射频混合相控。

数控接口板接收控制信号,包括开关切换信号、移相器和数控衰减信号(0.5 dB步进),及时配置TR组件。由于每个TR组件中衰减和移相控制字较多,可通过SPI总线接口形式减少接口引线。且在实际工作中,基带部分需要提前配置下次衰减和移相控制字,可实现与射频开关切换相同方式,即通过高低电平转换即可迅速完成对射频器件的控制,满足射频单元控制响应时间短(小于100 ns)的需求。

Figure 2. Structure of RF phased array antenna

图2. 射频相控阵天线结构

2.2. 宽带模拟数字转换与数字中频单元

该部分主要基于Xilinx公司的RFSoC芯片实现 [10]。RFSoC集成现场可编程门阵列(FPGA)、宽带模拟数字转换器(RF-ADC/RF-DAC)、高度灵活的软判决纠错编码(SD-FEC)模块、以及处理器系统(Processing System, PS)等。其中,模拟数字转换器作为系统数字中频的主要单元,由8个RF-ADC与8个RF-DAC组成,通过SMA缆线与射频单元直接相连进行信号传输,其内部结构与功能具体介绍如下。

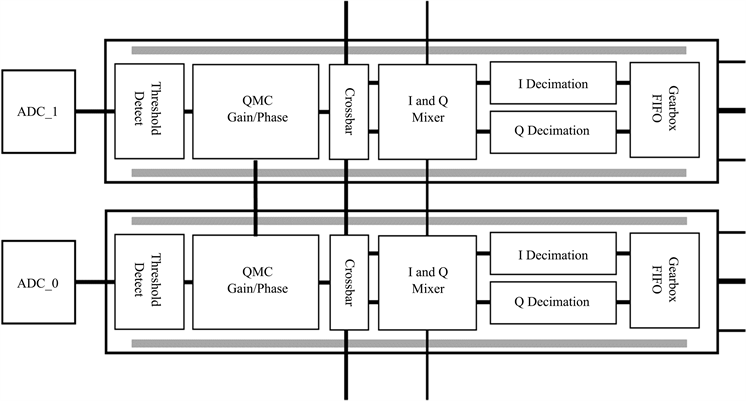

RF-ADC的原理示意图如图3所示,其内部结构还包含阈值检测(Threshold Detection)模块、正交调制校正(Quadrature Modulation Correction, QMC)模块、IQ混频模块、数控振荡器(NCO)、IQ分路抽取模块以及可编程FIFO模块,如图4所示。每个RF-ADC为12 bit精度,每2个RF-ADC组成1个子单元(tile),并配置锁相环(PLL)和必要的时钟逻辑,通过AXI4总线协议与PS端进行通信。在本原型系统中,RF-ADC将模拟中频信号变换为数字基带信号。采样数据首先经过输入门限检测输入模拟信号的功率,经过QMC模块对模拟信号进行幅度和相位增益补偿,进入数字下变频(Digital Down Conversion, DDC)模块进行I/Q下混频并抽取降低信号数量,最后经过可变数据缓冲器(Gearbox FIFO)进行时钟频率匹配并改变数据位宽,通过高速接口单元传递给系统融合计算单元处理。

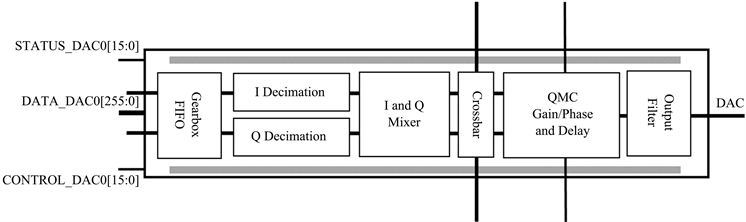

RF-DAC原理示意图如图5所示,其内部结构还包含可编程FIFO模块、IQ分路插值模块、IQ混频模块、数控振荡器(NCO)、QMC模块和输出滤波器模块,如图6所示。每个RF-DAC为14 bit精度,每4个RF-DAC组成1个子单元(tile),并配置锁相环(PLL)和必要的时钟逻辑,同样通过AXI4总线协议与PS端进行通信。在本原型系统中,RF-DAC将数字基带信号变换为模拟中频信号。数字信号首先经过数字上变频(Digital Up Conversion, DUC)模块完成内插滤波,升采样以及数字混频,然后经过逆SincFIR滤波器补偿并产生模拟输出,以差分形式互补输出两路模拟电流,电流之和等于RF-DAC满量程电流。

通过配置RF Data Converter IP核可以改变RF-ADC和RF-DAC的采样率、带宽、抽取倍数、AXI4总线时钟、每周期采样数、输入输出信号类型(Real信号或I/Q信号)以及对应的奈奎斯特区等参数,从而改变系统的参数设置和工作状态。本原型系统中关于IP核参数设置如表1所示。

Figure 3. Schematic diagram of RF-ADC

图3. RF-ADC原理示意图

Figure 4. Diagram of RF-ADC internal structure

图4. RF-ADC内部结构示意图

Figure 5. Schematic diagram of RF-DAC

图5. RF-DAC原理示意图

Figure 6. Diagram of RF-DAC internal structure

图6. RF-DAC内部结构示意图

Table 1. Parameters settings in RF data converter IP core

表1. RF数据转换器相关参数设置

2.3. X86 + FPGA融合计算单元

本文提出的原型系统利用配置Intel Xeon Gold 6154的通用服务器与Xilinx UltraScale + FPGA构成融合计算单元。通常情况下,各类大规模多波束无线通信原型系统的算法软件架构采用通用服务器或FPGA部署 [11]。X86通用服务器计算能力强、开发效率高、调试灵活性大,但实时数据处理速度有限,可支持的系统带宽有限 [12] [13];而FPGA虽然可实现实时数据高速并行处理,但编程周期较长,调试难度较大,在处理海量基带信号、实现动态波束成形方面有较大难度,也不适合用于通信算法快速验证 [14] [15]。对于本文提出的融合计算架构,通过模块化设计(Block Design)对FPGA进行编程,用于部署软件定义无线电(Software Defined Radio, SDR)相关算法;在多核X86通用服务器中采用高级语言以及并行指令集快速实现数据计算,满足高计算能力的同时获得高开发效率和强调试灵活性,可以应用于快速部署验证先进无线基带算法。

2.4. 高速接口单元

高速接口单元包含PCI-Express总线接口,GTY高速收发接口,Xilinx Aurora以及Alveo U200数据中心加速卡。其中,数据中心加速卡与X86服务器PCI-Express总线接口连接,可以提升服务器计算能力;Xilinx Aurora与RFSoC侧GTY高速接口相连,具有资源成本低、吞吐量可扩展、数据接口灵活等优点;数字中频单元(Xilinx Aurora)与融合计算单元(数据中心加速卡)之间通过QSFP (Quad Small Form-factor Pluggable)接口连接,每个QSFP数据传输速率可达25 Gbps,总速率可达100 Gbps。下行链路传输时,融合计算单元通过QSFP传输数据进入数字中频单元FIFO存储器,收发组帧模块将高速接口传输的基带信号按照定义的帧格式解包,分离得到用户数据和波束控制数据,其中用户数据传输至RF-DAC,波束控制数据经处理后成为高低电平信号,用于配置射频单元侧数控接口板,实现波束成形。上行链路传输时,数字中频单元中RF-ADC输出用户数据通过收发组帧模块按照定义帧格式打包,进入FIFO存储器后经QSFP及高速接口传输至融合计算单元。两种过程中,FIFO存储器均起到数据缓存和异步时钟域转换的作用。

3. 原型系统算法与软件实现

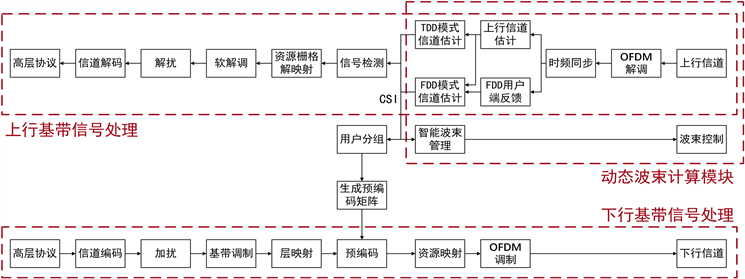

算法与软件架构完成基带信号处理、软件定义数字中频功能。其中基带信号处理包括上行基带信号处理、下行基带信号处理及动态波束计算模块,其流程如图7所示。

Figure 7. Flow chart of baseband signal processing

图7. 基带信号处理示意图

下行基带信号处理过程中,比特流数据从基站MAC层下发至物理层,再经过信道编码、序列加扰、基带调制、层映射、与编码、资源映射、OFDM调制等功能模块处理,生成待发数据。具体而言,信道编码采用LDPC编码方案,将编码比特序列与加扰序列相乘,形成加扰比特块后转换为复值调制符号块,本系统可支持包括BPSK、QPSK、16-QAM、64-QAM以及256-QAM的5种调制方案,并通过层映射分配多个传输层,经过预编码映射天线端口,完成资源映射后以OFDM符号的形式发送进入无线信道。上行基带信号处理过程中,通过高速数据接口与数据流转发单元,接收来自RFSoC的数据,经过OFDM解调、时频同步、信道估计、信号检测、资源栅格解映射、解层映射、软解调、解扰、信道译码等功能模块处理,得到用户数据。动态波束计算模块在实现动态波束计算之前,需要接收并处理上行链路用户数据,分析获得基站与用户之间的信道状态信息(CSI)。且相比于瞬时信道状态信息(iCSI),统计信道状态信息(sCSI)在满足精确度要求的条件下变化缓慢且容易获得。在获取信道状态信息后通过相应的通信算法实现信道信息预测、波束管理及波束成形等,进而产生调整波束指向、宽度、能量的多波束控制数据。

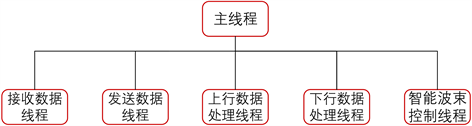

X86服务器内部利用到多线程技术,各线程独立运行、适当交互,从而实现并行计算,其软件架构由主控制线程、接收数据线程、发送数据线程、上下行数据处理线程等构成,如图8所示。其中接收数据线程与发送数据线程分别与上下行数据处理线程进行数据交互,上下行数据处理线程分别由多个子线程构成,共同完成基带信号处理功能,同时还可以集成信道估计、波束管理、波束控制等算法。动态波束计算线程主要对用户数据进行分析处理,产生波控数据从而实现动态多波束控制。同时,X86通用服务器还利用高级语言单指令多数据流技术(Single Instruction Multiple Data, SIMD)和Intel数学核心函数库(Intel Math Kernel Library, MKL)。SIMD技术可以大幅提高程序执行速度,高效地利用多核服务器的资源;MKL库函数提供了包括线性代数、快速傅里叶变换、矢量数学等多种工具包,大幅提高无线通信基带算法处理的性能,优化服务器处理速度,为本系统程序设计与实现提供有力支持。

Figure 8. Multithreading software architecture of X86

图8. X86多线程软件架构

4. 原型系统实验验证结果

本系统作为5G向6G演进的宽带动态多波束原型验证系统,设计上与主流波束域标准相一致。本系统设定基站端配置512根天线,共8个数字通道,支持8波束动态通信,可以服务1~8个用户终端,射频模块采样率为3.93216GSPS,可支持400 MHz有效通信带宽,FFT大小为4096,子载波间隔为120 KHz,提供5种可选的调制方式,以及两种长度的循环前缀。本原型验证系统性能指标如表2所示。可以看出,本系统在满足多天线和大带宽的条件下还可以进一步实现动态多波束成形,在下一代移动通信系统研发中具有很好的实验和验证意义。

为了验证本系统在实际应用中的可靠性与有效性,本小节呈现了系统在不同信道条件下传输误块率(Block Error Bit, BLER)、误码率(Bit Error Rate, BER)性能曲线以及吞吐量数据。在可靠性测试中,设置仿真时隙数为2000,总传输比特数为1.63952 × 108,传输块数为2000,测得系统在不同信道条件下的误块率曲线和误码率曲线如图9所示。

Table 2. Performance index of prototype system

表2. 原型系统性能指标

Figure 9. Performance comparison of BLER and BER of 1Tx-1Rx link under different channel conditions

图9. 1发1收链路在不同信道条件下的误块率(BLER)和误码率(BER)性能对比图

Table 3. Throughput performance of 1Tx-1Rx system with 400 MHz effective bandwidth under different MCS

表3. 400M有效带宽1发1收系统在不同MCS下的吞吐量性能

可以看出,LS信道估计性能与理想信道估计性能差距较大,且随着误码率降低,误块率仍然较高。由于在仿真过程中认为信道沿着子载波方向变化缓慢,因此可以考虑对相邻几个子载波上的信道系数取平均以改善信道估计性能。由图中可见,通过在一个RB上对估计出的信道系数取平均,减小了噪声对信道估计准确度的影响,使得LS估计的性能较为接近理想信道估计缺陷。在有效性测试中,对系统在不同MCS方案和不同调制阶数的条件下,分别测得链路发送、接收时间以及吞吐量,结果如表3所示。

5. 结束语

移动通信技术发展已进入B5G和6G时代,面对未来全球广域的多场景用户宽带接入需求,动态多波束通信已成为构建空天地海一体化互联网络的关键使能技术之一。面对动态多波束技术中关键环节和先进算法的验证需求,本文设计了宽带动态多波束无线通信原型系统用于实验。本系统利用X86通用服务器与FPGA融合计算架构部署无线基带算法,利用RFSoC完成多通道宽带模数/数模转换和数字中频,可以支持智能动态波束成形,并具有带宽大、吞吐量高、算法快速部署等优点,涵盖了无线通信系统上、下行链路基站侧与用户侧的各个环节。同时,本文还给出系统可靠性和有效性测试。在面向未来6G通信系统和卫星通信系统的开发中可以用于关键技术验证和先进通信算法快速部署,具有重要的实用意义。