摘要: 一直以来,传统的红绿灯是采用固定时长方式进行路面交通控制,是成熟有效的系统,具有通行效率不高的缺点。为优化路口的车辆通行,本文设计了一种自动感知的交通光控制器系统(ATLC),对道路交通流进行了研究。该方法利用通行高峰和低谷不同数据,可以有效地减少非高峰时段的等待时间,包括紧急情况和VIP车辆通行以及行人的安全也都可考虑在内。本文设计的低成本自动交通灯控制系统,为地面通行提供了稳定的交通流量。该系统利用VHDL语言进行开发,使用时序仿真进行测试。该系统能够检测不同时刻车辆通过率,调节相对应的交通灯时间长度随之变化,实现对红绿灯的智能调节。利用此智能调节控制路面交通,可使主支干道协调配合,从而提高路口的通行效率。

Abstract:

For all the times, the traditional method of fixed length of traffic light for road traffic control has long been a proven and effective system, but it has the disadvantage of low traffic efficiency. In or-der to optimize traffic at intersections, a traffic light controller (ATLC) system based on flow sensing is studied, and the traffic flow is discussed. This method takes advantage of peak and slump trough traffic slots to effectively reduce waiting times during off-peak hours, including emergencies and VIP vehicle passes and pedestrian safety. The low-cost automatic traffic light control system de-signed in this paper provides a stable traffic flow for ground traffic. The system is developed with VHDL and tested by time series simulation. The system can realize the intelligent regulation of the traffic light, detect the arrival rate of vehicles at different times, so that the corresponding length of the traffic light configuration time changes accordingly, so as to intelligently regulate and control the road traffic, so that the main and branch roads coordinate, thus improving the efficiency of the intersection.

1. 引言

近年来,智慧城市的发展对与城市的可持续发展至关重要 [1]。当今城市面临的主要问题是交通拥堵,交通堵塞造成交通行成本的上升,并且影响人们的日常生活 [2]。交通拥堵是世界上许多城市面临的严重问题。在全球最主要、繁忙的城市中,交通拥堵已经引起了研究人员的重视。交通拥堵直接影响了出行成本、人力成本和市场成本,间接抬高了商品价格 [3]。为了解决这些交通问题,我们必须建立新的便利设施和基础设施,但同时设法让这些设施智能化,这将为缓解交通提供新的途径 [4]。

在十字路口通常会设置交通灯或交通信号,以便控制交通 [5]。这是一种安装在十字路口的电子系统,以预先定义的颜色系统(通常是红、黄、绿)来控制车、人的通行 [6]。交通灯控制器TLC (TLC)可用ASIC、FPGA和微控制器系统实现 [7] - [12]。FPGA相对于微控制器,在I/O端口的数量、处理速度和性能等方面具有优势。所有这些优势在TLC设计中都是非常关键的 [13]。在TLC的设计中,成本也是一个非常重要的问题。FPGA的使用可以降低成本 [14] [15]。

本文介绍基于的FPGA的交通灯控制器设计,采用VHDL语言进行编写,并且结合Quartus II软件进行系统设计与调试 [16]。FPGA获取当前通过十字路口的车辆的信号,并根据这些信号发送下一步命令。在特定道路上,应设置特别的交通信号灯。另外,FPGA还需要考虑时间 [17] [18] [19] [20]。在本文中,我们可以在每个方向上以一定距离放置三个传感器,我们可以假设第一个传感器流量较低,第二个传感器给出中等流量,第三个给出高流量,根据传感器的状态,我们可以在特定方向上分配不同颜色交通灯的指示时间。在本文中,我们可以假设四种道路交通中的传感器位置,实现各种不同情况,开发这些情况下电路的VHDL代码。

2. 设计原理

2.1. 交通灯控制规则

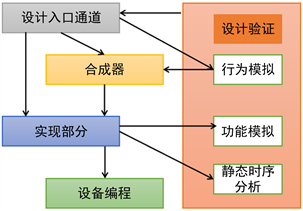

FPGA的设计流程见如下流程图。图1为FPGA设计流程的简化版本。

Figure 1. Schematic diagram of FPGA-based design flow

图1. 基于FPGA的设计流程图

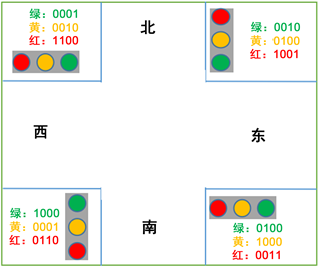

交通灯控制器可以从一些任意的假设状态开始设计。比如首先假设向北方向的车辆被允许通行,然后在东、南、西方向的车辆被允许依次移动。编写交通灯控制器程序的优点是,在一个程序中,可以很容易地根据需要进行修改,即假设主干道上的通行时间更多,支路通行时间更少;时钟划分为主要道路时钟时间更多,支路时钟时间更少,这是因为主要道路交通比支路交通繁忙。一般来说,TLC系统在每个方向都有三个灯(红色、绿色、黄色),红灯表示停止通行,绿灯表示允许通行,黄色灯表示将在几秒钟内停止通行。图2表示交通灯系统控制规则。

Figure 2. Traffic light system control rules

图2. 交通灯系统控制规则

2.2. 设计方法及实现

图3为交叉口处的交通信号示意图。在该结构中,有四个方向的交通信号,北、南、西、东分别由R1、R2、R3和R4表示。假设南北方向为主干道,东西方向为支干道。

Figure 3. Schematic diagram of traffic signals at intersections

图3. 交叉路口的交通信号示意

首先,所有信号控制器处于置0模式,其中道路信号(R1)为绿色,其他道路R2、R3和R4均为红色。我们已将这个状态指定为S0。之后,控制器发送控制信号,使状态变为S1,其中R1为黄色,而其他信号仍然为红色。在此状态下,控制器X2检查R2处的传感器信号是否为低电平即R2处是否有车辆。如果传感器给出该道路上没有车辆的信号,则信号将控制状态使其转移到S4,表示道路R3上的信号变化,而其余信号显示为红色。另一方面,如果道路R2上存在车辆,则状态转换为S2,此时道路R2上的信号切换为绿色,其余的信号只有在状态S2显示绿色信号后,道路R2上的信号从绿色变为黄色,而所有其他信号继续处于红色状态。当控制器处于S3状态时,它检查在道路R3上的传感器X3的响应。如果传感器的输出为低电平,系统将转移到状态S6,否则转到相应的下一个状态S4。另一方面,在S4时,当道路R3的交通信号变为绿色时,道路R1、R2和R4的信号本身仍保持红色,这时将转移到状态S5。当控制器的状态为S5时,它检查道路R4上的传感器X4的输出。根据X4的输出,进一步的状态也会发生相应的变化。如果传感器输出值为低,则控制被转移到状态S0。当控制器处于S5状态时,道路R3上的信号从绿色变为黄色。当控制状态为S6时,道路R4的信号变成绿色,而所有信号只保持红色信号。然后转移到状态S0。在状态S7中,道路R4的信号从绿色变成黄色。同时,检查作为X1的第一道路R1上的传感器的输出。如果X1输出信号为低,则转移到状态S2,否则转移到初始状态S0。以上这些控制信号的状态并不是固定的,用户可以指定状态数、交通灯的顺序和交通灯延迟时间,这是设计的优势之一。

2.3. TLC状态转换

TLC系统的状态转换主要是在模式控制信号mode的作用下工作。控制信号有四种可能值,包括2个峰值模式和非峰值模式下的有限状态机(FSM),以及针对紧急模式提出的2种状态。峰值模式有5个输入和20个输出,同时有12个状态和48个转换方向。同样地,非峰值模式有11个输入和20个输出,12个状态和149个转换方向。该信息将在合成过程中生成。状态转换从mode取不同值开始。状态图的右侧为峰值模式FSM,在高峰时段将执行该FSM。这个状态将一直持续到mode信号改变。在这个FSM中,每个绿灯状态之间有两个中间状态,即黄灯和红灯状态。红灯状态在黄灯之后执行。当紧急情况发生时,将通过更改mode值使进入紧急模式。

3. 结果与分析

3.1. RTL实现及验证

本项目划分为四大模块:1) 控制模块;2) 计时器模块;3) 时钟分频模块;4) 交通灯显示驱动模块。

控制模块:该模块是整个交通灯芯片的CPU。可控制UART通信模块,可读取寄存器,判断工作模式,并相应的改变交通灯状态和通行时间。输出控制信号驱动显示模块进行显示。

计时器模块:计时器模块的基础为计数器,计数器可以对脉冲的个数进行计数,经过时钟分频模块将系统时钟的50 Mhz的工作频率分频为计时器模块的工作频率1 Mhz后,对每一次的脉冲进行计数,控制模块将发送每个模式所需要计数的时间给计时器模块,当计时器倒数归零则促使控制模块进入下一个模式,而计时器所计数的时间将发送给数码管进行显示。

时钟分频模块:在FPGA中一般以晶振作为时钟源,接入到分频器当中。晶振所产生的时钟信号是周期固定的,在需要其他周期时就需对现已有的时钟信号进行分频,分频是将信号的周期变大,频率变小,以满足设计者所需时钟信号周期。为了与智能交通控制系统中的信号周期相匹配,需要将系统频率转换为周期以秒计时的单位。本系统中我们将时钟频率固定为1 MHz,分频模块能够将1 MHz的时钟信号分频为1 Hz,来驱动后续模块进行工作。

数码管扫描模块:数码管扫描模块将接收由控制模块发送的各个模式需要显示在数码管上的数据,如不同颜色灯的计时时间,并会按照计时器模块上的数值采用动态扫描的方式点亮相应的数码管。

3.2. FPGA实验结果

根据仿真实验结果,当到达率λ = 0.03时,对应的平均通行时间即智能交通控制系统中的直行绿灯时长为18 s,当到达率λ = 0.02时,对应左转绿灯时长为10 s,则红灯时长为34 s;当到达率λ = 0.037时,直行绿灯时长为30 s,当到达率λ = 0.02时,对应左转绿灯时长为12 s,红灯时长为50 s。start为触发信号,当start为低电平时,系统为初始清零状态,即所有方向交通灯均为红灯,当start为高电平时,系统进入正常信号转换状态,完成主支干道的信号灯指示任务。main_straight_green_light是主干道由到达率所对应的平均等待时间,即依据交通规则计算出的绿灯时间长度,main_straight_green_light_count则是由所接收到的数据完成计时工作,在不同的到达率下,绿灯时间数据会根据到达率的改变而智能改变;access_straight_green_light是支干道直行绿灯时间,同样是根据支干道所获得的平均等待时间即直行绿灯的通行时间长度;其他相位的交通信号灯同样依据此原理。1表示为左转绿灯,2表示为直行绿灯,4表示为黄灯,8表示为红灯,A为南北向,B为东西向。由仿真实验可知:南北向的红灯时长为东西向的直行绿灯、左转绿灯以及黄灯的时长之和,交通灯在完成信号转换功能的同时,同样需要完成相应信号灯的时间倒计时功能,东西方向亦是。在南北向为绿灯状态时,东西向为红灯状态,南北向的直行绿灯倒计时结束后,信号灯转换为黄灯,黄灯倒计时完毕后,左转绿灯的信号开始完成倒计时功能,在左转绿灯倒计时结束后,信号灯转换为黄灯,当作为缓冲的黄灯倒计时结束后,信号灯转换为红灯,直到红灯倒计时结束,南北向一个周期的交通灯指示完成,东西向亦是如此。

3.3. 静态时序分析和综合分析

静态时序分析:静态时序分析(Static Timing Analysis)是一种验证方法。它采用穷举分析方法,提取电路时序路径并计算延迟,检查信号的建立时间和保持时间是否满足设计要求。通过对最大路径和最小路径延迟的分析找出违背时序约束的错误。静态时序分析常用软件是Synopsys公司的PrimeTime。

物理综合:完成了逻辑综合后,相当于完成了前端设计的工作,并生成了具有逻辑功能的门级网表。但目前为止我们所做的都是基于逻辑和代码的设计,并未涉及到物理层面的设计,此时对芯片性能的分析也只是基于算法和计算机模拟的结果,并没有实际的物理意义。因此为了产生真正符合工艺要求,可以进行流片生产的设计文件,我们需要进行后端验证的工作。第一步就是使用物理综合工具,根据门级网标文件和约束,并利用工艺厂商提供的物理库,进行布局、时钟树综合和布线。这种方法是用比较接近真实的物理信息计算时间参数,综合后的电路接近最优,综合报告能比较真实地反映电路的状态。一般采用的物理综合工具为Synopsys公司的IC Compiler。

3.4. DRC设计规则检查

满足设计规则的芯片才能保证版图满足厂家流片的要求。设计规则是版图中个图形尺寸的规范。一般设计规则是以器件的特征尺寸为基准,根据制造工艺水平及其他考虑,制定出的一套各层掩膜板上图形尺寸的许可范围。设计中采用ICC中的DRC检查工具Hercules进行检查。

4. 结论与讨论

现代的多路交通管理方式在很大程度上改善了交通状况。先进的信号控制器有助于改善城市交通,这与控制器的复杂度成正比。使用状态控制系统可以很好地处理这些复杂的控制器。减少状态控制器有助于减少所需的硬件系统,从而实现低功耗和高效的设计系统。基于FPGA的智能交通系统未来目标是可以通过使用更多智能的电路系统来直接实时应用。这项工作可以进一步扩展到其他FPGA系列,以实现速度升级,并使用aurdino处理器和raspberry pi来改善诸如速度之类的参数,以实现更好的性能。本文依照道路交通情况,设计出基于FPGA的智能交通灯控制系统的结构框架,并分别完成各个模块的结构设计。将其运用到智能交通控制系统中,有很高的实用性及高效性。

本设计采用VHDL硬件语言描述,使用分模块设计的方法实现了交通灯交替开启和倒计时时间的显示系统,以及车辆和行人安全通过的命令实现。程序数据可根据实际情况进行灵活设置。将来我们会完成后续工作,比如物理综合。综合时可以兼顾电路面积的情况,可以调整电路结构和布局,使之在时间和面积之间寻求最大限度的折中,达到最优点。